Abstract

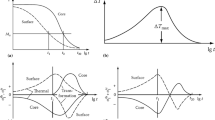

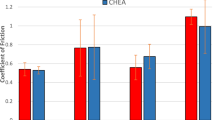

The present work attempts to determine an appropriate design of double-sided adhesive tape, which plays a significant role in defining the degree of chip surface damage in a plastic LOC (lead-on-chip) package. Various tape designs were tested to determine their effectiveness in preventing thermal stress-related damage on the chip surface during temperature cycling. The experimental results indicate that the thermomechanical stability of the IC pattern is more influenced by whether the LOC tape is employed along the chip edge than by the size of the tape covering area. Moreover, it was found that chip surface damage associated with LOC tape can be caused by normal stress applied to the chip surface vertically as well as by shear stress, which is known to cause damage. The importance of the normal stress component is verified through a 3-dimensional FEM (finite element method) simulation adopted to define the thermal stress distribution in the present LOC package. The numerical calculation shows that when the tape is designed to cover the chip corner, the magnitude of normal stress reveals a maximum value at the edge of the chip.

Similar content being viewed by others

References

S. M. Lee, J. H. Lee, S. Y. Oh, and H. K. Chung,45 th ECTC, p. 455,IEEE, LasVegas, NE (1995).

S. M. Lee and K. W. Lee,Jpn, J. Appl. Phys,35, 5462 (1996).

M. Lamson, D. Edwards, S. Groothuis, and G. Heinen,43 th ECTC, p. 1045, IEEE, Seattle, WA (1993).

S. M. Lee,Jpn. J. Appl. Phys. 41, 3860 (2004).

S. M. Lee,Met. Mater.-Int. 9, 489 (2003).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Lee, SM. Thermomechanical stability of memory package with LOC structure. Met. Mater. Int. 11, 89–93 (2005). https://doi.org/10.1007/BF03027490

Issue Date:

DOI: https://doi.org/10.1007/BF03027490