Abstract

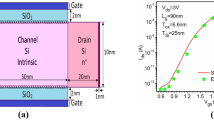

Tunnel Field Effect Transistors (TFET) based on quantum mechanical band to band tunneling (BTBT) are promising alternatives for low power analog applications. Additionally, the concept of junctionless (JL) devices realized by the charge plasma concept offers added advantages in terms of simplified fabrication techniques. In n type JL-TFET, p+ source is induced using a polarity gate (PG) with suitable work function. However, retention of induced p+ source is not a sole contribution of PG, the source electrode (SE) metal silicide work function also plays a significant role in the retention of hole plasma (specially near the interface of SE/induced source). Thorough study regarding the combined influence of PG and SE metal silicide work function on induced p+ source is missing in the literatures. This work explores the performance of JL-TFET of different SE metal silicide such as TiSi2 (4.53 eV), CrSi2 (4.85 eV) and Pd2Si (5.3 eV). It is perceived that for SE metal silicide with work function lower than p+ induced source i.e., TiSi2 and CrSi2 the depletion of hole plasma (formation of Schottky interface) appears near the SE/p+ induced source interface. The depletion of hole plasma is attributed to the combined electric field of SE metal silicide and the PG, the immediate consequence is the refrainment of current. Further, due to the formation of Schottky interface for TiSi2 and CrSi2, the performance of the device is examined by revoking and evoking the Universal Schottky Tunneling (UST) model. Results reveal the undervalued performance of the device without the inclusion of UST, primarily a lower drain current (and thereby the analog performance) of the device is obtained, since it ignores the Schottky tunneling at SE/p+ induced source interface. However, the inclusion of UST model emulates the performance of JL-TFET precisely, by incorporating the Schottky tunneling at the SE/p+ induced source interface. Thus, for the retention of hole plasma, appropriate SE work function i.e., ΦSE > Φp+ induced source is required, whereas for SE work function ΦSE < Φp+ induced source appropriate Schottky tunneling must be considered for accurate analysis of the device. The study also reveals that the depletion of hole plasma and hence the formation of Schottky interface can be avoided using SE with metal work function source for which consideration of UST is immaterial.

Similar content being viewed by others

References

Y. Goswami, B. Ghosh, P.K. Asthana, Analog performance of Si junctionless tunnel field effect transistor and its improvisation using III–V semiconductor. RSC Adv. 4, 10761–10765 (2014)

P.K. Asthana, B. Ghosh, Y. Goswami, B.M.M. Tripathi, High-speed and low-power ultradeep-submicrometer III-V heterojunctionless tunnel field-effect transistor. IEEE Trans. Electron. Devices 61, 479–486 (2014)

B. Ghosh, M.W. Akram, Junctionless tunnel field effect transistor. IEEE Electron. Device Lett. 34, 584–586 (2013)

K. Nigam, P. Kondekar, D. Sharma, B.R. Raad, A new approach for design and investigation of junction-less tunnel FET using electrically doped mechanism. Superlattices Microstruct. 98, 1–7 (2016)

N. Damrongplasit, S.H. Kim, T.-J.K. Liu, Study of random dopant fluctuation induced variability in the raised-Ge-source TFET. IEEE Electron. Device Lett. 34, 184–186 (2013)

S. Tirkey, D.S. Yadav, D. Sharma, Controlling ambipolar current of dopingless tunnel field-effect transistor. Appl. Phys. A 124, 809 (2018)

M. Vadizadeh, Performance estimation of junctionless field effect diode. Appl. Phys. A 125, 495 (2019)

J. Madan, R. Chaujar, Numerical simulation of N+ source pocket PIN-GAA-tunnel FET: impact of interface trap charges and temperature. IEEE Trans. Electron. Devices 64, 1482–1488 (2017)

J. Madan, R. Chaujar, Gate drain-overlapped-asymmetric gate dielectric-GAA-TFET: a solution for suppressed ambipolarity and enhanced ON state behavior. Appl. Phys. A 122, 973 (2016)

S. Shekhar, J. Madan, R. Chaujar, Source/gate material-engineered double gate TFET for improved RF and linearity performance: a numerical simulation. Appl. Phys. A 124, 739 (2018)

J. Madan, R. Chaujar, Temperature associated reliability issues of heterogeneous gate dielectric—gate all around—tunnel FET. IEEE Trans. Nanotechnol. 17, 41–48 (2018)

M.S. Parihar, D. Ghosh, G.A. Armstrong, R. Yu, P. Razavi, A. Kranti, Bipolar effects in unipolar junctionless transistors. Appl. Phys. Lett. 101, 093507 (2012)

R.J. Hueting, B. Rajasekharan, C. Salm, J. Schmitz, The charge plasma PN diode. IEEE Electron. Device Lett. 29, 1367–1369 (2008)

S. Gupta, K. Nigam, S. Pandey, D. Sharma, P.N. Kondekar, Effect of interface trap charges on performance variation of heterogeneous gate dielectric junctionless-TFET. IEEE Trans. Electron. Devices 64, 4731–4737 (2017)

S.B. Rahi, B. Ghosh, High-k double gate junctionless tunnel FET with a tunable bandgap. RSC Adv. 5, 54544–54550 (2015)

S. Tirkey, K. Nigam, S. Pandey, D. Sharma, P. Kondekar, Investigation of gate material engineering in junctionless TFET to overcome the trade-off between ambipolarity and RF/linearity metrics. Superlattices Microstruct. 109, 307–315 (2017)

H. Aghandeh, S.A.S. Ziabari, Gate engineered heterostructure junctionless TFET with Gaussian doping profile for ambipolar suppression and electrical performance improvement. Superlattices Microstruct. 111, 103–114 (2017)

P.K. Asthana, Y. Goswami, S. Basak, S.B. Rahi, B. Ghosh, Improved performance of a junctionless tunnel field effect transistor with a Si and SiGe heterostructure for ultra low power applications. RSC Adv. 5, 48779–48785 (2015)

T.J. Drummond, Work functions of the transition metals and metal silicides (Albuquerque, Sandia National Labs, 1999)

Atlas Users Manual 2010 Silvaco Santa Clara CA

A. Biswas, S.S. Dan, C. Le Royer, W. Grabinski, A.M. Ionescu, TCAD simulation of SOI TFETs and calibration of non-local band-to-band tunneling model. Microelectron Eng 98, 334–337 (2012)

J. Madan, R. Chaujar, Gate drain underlapped-PNIN-GAA-TFET for comprehensively upgraded analog/RF performance. Superlattices Microstruct. 102, 17–26 (2017)

K. Matsuzawa, K. Uchida, A. Nishiyama, A unified simulation of Schottky and ohmic contacts. IEEE Trans. Electron. Devices 47, 103–108 (2000)

Acknowledgements

Authors would like to acknowledge the members of VLSI center of excellence, Chitkara University, Punjab, India and Department of Applied Physics, Delhi Technological University, Delhi for continuous support during the preparation of the manuscript.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Madan, J., Pandey, R., Sharma, R. et al. Impact of metal silicide source electrode on polarity gate induced source in junctionless TFET. Appl. Phys. A 125, 600 (2019). https://doi.org/10.1007/s00339-019-2900-6

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-019-2900-6