Abstract

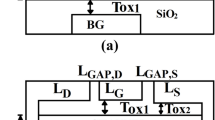

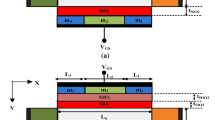

This paper presents a mathematical modeling insight for the novel heterogate dielectric-dual material gate-GAA TFET (HD-DMG-GAA-TFET) and validating the results with TCAD simulation. By using the appropriate boundary conditions and continuity equations, the Poisson’s equation is solved to obtain the potential profile. The developed model is used to study the analog performance parameters such as subthreshold swing (SS), threshold voltage (Vth), transconductance (gm), drain conductance (gd), device efficiency (gm/Ids), intrinsic gain (gm/gd), channel resistance (Rch) and output resistance (Ro). Further, to optimize the effect of metal work function on analog performance, three different combinations of DMG configurations has been studied. The results demonstrated that for a difference of 0.4 eV, the analog performance of the device is optimized. Low off current and high value of on current resulting into a higher ION/IOFF ratio has been obtained, which is appropriate for sub-nanometre devices and low standby power applications. The analytical results obtained from the proposed model shows good agreement with the simulated results obtained with the ATLAS device simulator.

Similar content being viewed by others

References

ATLAS User’s Manual (2014) SILVACO Int., Santa Clara, CA

Bhuwalka KK, Born M, Schindler M, Schmidt M, Sulima T, Eisele I (2006) P-channel tunnel field-effect transistors down to sub-50 nm channel lengths. Jpn J Appl Phys 45:3106–3109. doi:10.1143/JJAP.45.3106

Born M, Bhuwalka KK, Schindler M, Abelein U, Schmidt M, Sulima T, Eisele I (2006) Tunnel FET: a CMOS device for high temperature applications. In: Proceedings of 25th international conference on microelectronics, Belgrade, Serbia and Montenegro, pp 124–127. doi:10.1109/ICMEL.2006.1650911

Boucart B, Ionescu AM (2007a) Length scaling of the double gate tunnel FET with a high-K gate dielectric. Solid-State Electron 51(12):1500–1507. doi:10.1016/j.sse.2007.09.014

Boucart K, Ionescu AM (2007b) Double gate tunnel FET with high-k gate dielectric. IEEE Trans Electron Devices 54(7):1725–1733. doi:10.1109/TED.2007.899389

Cho S, Sun MC, Kim G, Kamins TI, Park BG, Harris JS (2011) Design optimization of a type-I heterojunction tunneling field-effect transistor (I-HTFET) for high performance logic technology. J Semicond Technol Sci 11(3):182–189. doi:10.5573/JSTS.2011.11.3.182

Choi KM, Choi WY (2013) Work-function variation effects of tunneling field-effect transistors (TFETs). IEEE Electron Device Lett 34(8):942–944. doi:10.1109/LED.2013.2264824

Choi WY, Lee W (2010) Hetero-gate-dielectric tunneling field-effect transistors. IEEE Trans Electron Devices 57(9):2317–2319. doi:10.1109/TED.2010.2052167

Conde AO, Garcia-Sanchez FJ, Muci J, Sucre-Gonzalez A, Martino JA, Agopian PGD, Claeys C (2014) Threshold voltage extraction in tunnel FETs. Solid-State Electron 93:49–55. doi:10.1016/j.sse.2013.12.010

Fukuda K, Mori T, Mizubayashi W, Morita Y, Tanabe A, Masahara M, Yasuda T, Migita S, Ota H (2013) A compact model for tunnel field effect transistors incorporating nonlocal band to band tunneling. J Appl Phys 114(14):144512. doi:10.1063/1.4824535

Gandhi R, Chen Z, Singh N, Banerjee K, Lee S (2011) CMOS-compatible vertical-silicon-nanowire gate-all-around p-type tunneling FETs with ≤ 50-mV/decade subthreshold swing. IEEE Electron Device Lett 32(11):1504–1506. doi:10.1109/LED.2011.2165331

Hraziia Vladimirescu A, Amara A, Anghel C (2012) An analysis on the ambipolar current in Si double–gate tunnel FETs. Solid-State Electron 70:67–72. doi:10.1016/j.sse.2011.11.009

Jhaveri R, Nagavarapu V, Woo JCS (2010) Effect of pocket doping and annealing schemes on the source-pocket tunnel field-effect transistor. IEEE Trans Electron Devices 58(1):80–86. doi:10.1109/TED.2010.2089525

Lee DS, Yang HS, Kang KC, Lee JE, Lee JH, Cho S, Park BG (2010) Simulation of gate-all-around tunnel field-effect transistor with an n-doped layer. IEICE Trans Electron 93-C(5):540–545. doi:10.1587/transele.E93.C.540

Lee JS, Choi WY, Kang IM (2012) Characteristics of gate-all-around hetero-gate-dielectric tunneling field-effect transistors. Jpn J Appl Phys 51:06FE03. doi:10.1143/JJAP.51.06FE03

Madan J, Gupta RS, Chaujar R (2014) Influence of heterogeneous gate dielectric on hetero-dielectric-DMG-GAATFET for improved tunneling current. Int J Adv Technol Eng Sci 2(1):41–47

Madan J, Gupta RS, Chaujar R (2015a) Analytical drain current formulation for gate dielectric engineered dual material gate-gate all around-tunneling field effect transistor. Jpn J Appl Phys 54:094202. doi:10.7567/JJAP.54.094202

Madan J, Gupta RS, Chaujar R (2015b) Threshold voltage model of a hetero gate dielectric dual material gate GAA Tunnel FET. Advanced manufacturing, electronics and microsystems: techconnect Briefs 2015, pp 254–257. doi:10.13140/RG.2.1.3081.2003

Mallik A, Chattopadhyay A (2011) Drain-dependence of tunnel field-effect transistor characteristics: the role of the channel. IEEE Trans Electron Devices 58(12):4250–4257. doi:10.1109/TED.2011.2169416

Mookerjea S, Krishnan R, Datta S, Narayanan V (2009) Effective capacitance and drive current for tunnel FET (TFET) CV/I estimation. IEEE Trans Electron Devices 56(9):2092–2098. doi:10.1109/TED.2009.2026516

Nirschl T, Henzler S, Fischer J, Fulde M, Bargagli-Stoffi A, Sterkel M, Sedlmeir J, Weber C, Heinrich R, Schaper U, Einfeld J, Neubert R, Feldmann U, Stahrenberg K, Ruderer E, Georgakos G, Huber A, Kakoschke R, Hansch W, Schmitt-Landsiede D (2006) Scaling properties of the tunneling field effect transistor (TFET): device and circuit. Solid-State Electron 50:44–51. doi:10.1016/j.sse.2005.10.045

Noguchi M, Kim SH, Yokoyama M, Ichikawa O, Osada T, Hata M, Takenaka M, Takagi S (2015) High Ion/Ioff and low subthreshold slope planar-type InGaAs tunnel FETs with Zn-diffused source junctions. J Appl Phys 118:045712-1–045712-15. doi:10.1063/1.4927265

Shaker A, Ossaimee M, Zekry A, Abouelatta M (2015) Influence of gate overlap engineering on ambipolar and high frequency characteristics of tunnel-CNTFET. Superlattices Microstruct. doi:10.1016/j.spmi.2015.08.008

Toh EH, Wang GH, Samudra G, Yeo YC (2007) Device physics and design of double-gate tunneling field-effect transistor by silicon film thickness optimization. Appl Phys Lett 90(26):263507–263510. doi:10.1063/1.2748366

Toh EH, Wang GH, Chan L, Sylvester D, Heng CH, Samudra GS, Yeo YC (2008) Device design and scalability of a double-gate tunneling field-effect transistor with silicon–germanium source. Jpn J Appl Phys 47(4S):2593–2597. doi:10.1143/JJAP.47.2593

Ying L, He Jin, Mansun C, Cai-Xia D, Yun Y, Wei Z, Wen W, Wan-Ling D, Wen-Ping W (2014) An analytical model for gate-all-around silicon nanowire tunneling field effect transistors. Chin Phys B 23(9):097102-1-6. doi:10.1088/1674-1056/23/9/097102

Acknowledgments

Authors would like to thank Microelectronics Research Lab, Department of Engineering Physics Delhi Technological University to carry out this work. One of the authors (Jaya Madan) would like to thank University Grants Commission, Govt. of India, for providing the necessary financial assistance during the course of this research work.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Madan, J., Gupta, R.S. & Chaujar, R. Mathematical modeling insight of hetero gate dielectric-dual material gate-GAA-tunnel FET for VLSI/analog applications. Microsyst Technol 23, 4091–4098 (2017). https://doi.org/10.1007/s00542-016-2872-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-016-2872-9