Abstract

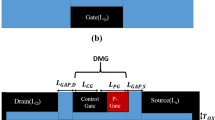

Although Tunnel Field Effect Transistors (TFET) offer low leakage current and allow good scalability, but they suffer from low ON-current. Present research paper focuses on the designing of an industry ready TFET that can operate efficiently at nano-scales allowing the fabrication of a smaller and more energy efficient overall device. To achieve the same, the Gate Metal Engineering (GME) and n+ Source Pocket (SP) schemes have been integrated on Double-Gate TFET (DG-TFET). For a distinct examination of the merits of GME and SP, 4 types of TFET architectures, namely the DG-TFET, GME-DG-TFET, SP-DG-TFET and GME-SP-DG-TFET (which amalgamates the merits of both GME and SP engineering) are investigated. All these device architectures are examined in terms of their electrical characteristics and analog parameters. GME-SP-DG-TFET (being superior among the four) is further analyzed under the presence of interface fixed charges (FC) of different polarity to affirm its reliability. Investigations of this device structure reveal that the positive FC are more noxious for the device as compared to negative FC. However, the enhanced flatband voltage under the negative FC translates to the high gate bias requirement to turn the device ON. Observance of only marginal variations in the parasitic capacitances and efficiency of the GME-SP-DG-TFET device in the presence of FC (both positive/negative) signifies its immunity and promises enhanced reliability. A remarkable improvement of the ION/IOFF by two order of magnitude (from 1010 to 1012) and a decrease in Vth by 27.71% observed for GME-SP-DG-TFET as compared to DG-TFET along with the improved reliability makes the former an efficient candidate for low power analog/RF applications.

Similar content being viewed by others

References

Biswal SM, Baral B, De D, Sarkar A (2019) Simulation and comparative study on analog/RF and linearity performance of III–V semiconductor-based staggered heterojunction and InAs nanowire (nw) Tunnel FET. Microsyst Technol 25(5):1855–1861

Boucart K, Ionescu AM (2007) Length scaling of the double gate tunnel FET with a high-k gate dielectric. Solid-State Electron 51:1500–1507

Cao W, Yao C, Jiao G, Huang D, Yu H, Li M-F (2011) Improvement in reliability of tunneling field-effect transistor with pnin structure. IEEE Trans Electron Dev 58:2122–2126

Choi WY, Park B-G, Lee JD, Liu T-JK (2007) Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Dev Lett 28:743–745

Cui N, Liang R, Xu J (2011) Heteromaterial gate tunnel field effect transistor with lateral energy band profile modulation. Appl Phys Lett 98:142105

Datta E, Chattopadhyay A, Mallik A, Omura Y (2020) Temperature dependence of analog performance, linearity, and harmonic distortion for a ge-source tunnel FET. IEEE Trans Electron Dev 67:810–815

Gnani E, Baravelli E, Gnudi A, Reggiani S, Baccarani G (2015) Capacitance estimation for InAs Tunnel FETs by means of full-quantum k· p simulation. Solid State Electron 108:104–109

Guillaumot B et al (2002) 75 nm damascene metal gate and high-k integration for advanced CMOS devices. In: Digest. International electron devices meeting, 2002. IEEE, pp 355–358

Jiao G et al (2009) New degradation mechanisms and reliability performance in tunneling field effect transistors. In: 2009 IEEE international electron devices meeting (IEDM), 2009. IEEE, pp 1–4

Joshi T, Singh Y, Singh B (2020) Extended-source double-gate tunnel FET with improved DC and analog/RF performance. IEEE Trans Electron Dev. https://doi.org/10.1109/ted.2020.2973353

Kim JH, Kim S, Park B-G (2019) Double-gate TFET with vertical channel sandwiched by lightly doped Si. IEEE Trans Electron Dev 66:1656–1661

Kumar N, Raman A (2019) Low voltage charge-plasma based dopingless tunnel field effect transistor: analysis and optimization. Microsyst Technol. https://doi.org/10.1007/s00542-019-04666-y

Lho YH, Kim KY (2005) Radiation effects on the power MOSFET for space applications. ETRI J 27:449–452

Li W, Woo JC (2020) Vertical P-TFET with a P-type SiGe pocket. IEEE Trans Electron Dev 67(4):1480–1484

Liu J, Wen H, Lu J, Kwong D-L (2005) Dual-work-function metal gates by full silicidation of Poly-Si with Co–Ni bi-layers. IEEE Electron Dev Lett 26:228–230

Long W, Ou H, Kuo J-M, Chin KK (1999) Dual-material gate (DMG) field effect transistor. IEEE Trans Electron Dev 46:865–870

Lu B, Lu H, Zhang Y, Zhang Y, Cui X, Lv Z, Liu C (2018) Fully analytical carrier-based charge and capacitance model for hetero-gate-dielectric tunneling field-effect transistors. IEEE Trans Electron Dev 65:3555–3561

Madan J, Chaujar R (2016) Interfacial charge analysis of heterogeneous gate dielectric-gate all around-tunnel FET for improved device reliability. IEEE Trans Dev Mater Reliab 16:227–234

Madan J, Chaujar R (2017a) Gate drain underlapped-PNIN-GAA-TFET for comprehensively upgraded analog/RF performance. Superlattices Microstruct 102:17–26. https://doi.org/10.1016/j.spmi.2016.12.034

Madan J, Chaujar R (2017b) numerical simulation of N+ source pocket PIN-GAA-tunnel FET: impact of interface trap charges and temperature. IEEE Trans Electron Dev 64:1482–1488

Madan J, Chaujar R (2018) Temperature associated reliability issues of heterogeneous gate dielectric—gate all around—tunnel FET. IEEE Trans Nanotechnol 17:41–48

Madan J, Gupta RS, Chaujar R (2017a) Mathematical modeling insight of hetero gate dielectric-dual material gate-GAA-tunnel FET for VLSI/analog applications. Microsyst Technol 23:4091–4098. https://doi.org/10.1007/s00542-016-2872-9

Madan J, Gupta RS, Chaujar R (2017b) Performance investigation of heterogeneous gate dielectric-gate metal engineered–gate all around-tunnel FET for RF applications. Microsyst Technol 23:4081–4090. https://doi.org/10.1007/s00542-016-3143-5

Madan J, Shekhar S, Chaujar R (2017c) Gate metal engineered heterojunction DG-TFETs for superior analog performance and enhanced device reliability. In: 2017 conference on information and communication technology (CICT). IEEE, pp 1–4

Mallik A, Chattopadhyay A (2012) Tunnel field-effect transistors for analog/mixed-signal system-on-chip applications. IEEE Trans Electron Dev 59:888–894

Marjani S, Hosseini SE (2015) Radio-frequency small-signal model of hetero-gate-dielectric pnpn tunneling field-effect transistor including charge conservation capacitance and substrate parameters. J Appl Phys 118:095708

Mookerjea S, Krishnan R, Datta S, Narayanan V (2009) On enhanced Miller capacitance effect in interband tunnel transistors. IEEE Electron Dev Lett 30:1102–1104

Mookerjea S, Mohata D, Mayer T, Narayanan V, Datta S (2010) Temperature-dependent I-V characteristics of a vertical In0.53Ga0.47As tunnel FET. IEEE Electron Dev Lett 31:564–566

Nagavarapu V, Jhaveri R, Woo JC (2008) The tunnel source (PNPN) n-MOSFET: a novel high performance transistor. IEEE Trans Electron Dev 55:1013–1019

Nirschl T et al (2006) Scaling properties of the tunneling field effect transistor (TFET): device and circuit. Solid State Electron 50:44–51

Pala M, Esseni D, Conzatti F (2012) Impact of interface traps on the IV curves of InAs tunnel-FETs and MOSFETs: a full quantum study. In: 2012 IEEE international electron devices meeting (IEDM), 2012. IEEE, pp 6.6.1–6.6.4

Poindexter EH (1989) MOS interface states: overview and physicochemical perspective. Semicond Sci Technol 4:961

Polishchuk I, Ranade P, King T-J, Hu C (2001) Dual work function metal gate CMOS technology using metal interdiffusion. IEEE Electron Dev Lett 22:444–446

Pradhan K, Mohapatra S, Sahu P, Behera D (2014) Impact of high-k gate dielectric on analog and RF performance of nanoscale DG-MOSFET. Microelectron J 45:144–151

Qiu Y, Wang R, Huang Q, Huang R (2014) A comparative study on the impacts of interface traps on tunneling FET and MOSFET. IEEE Trans Electron Dev 61:1284–1291

Sant S, Moselund K, Cutaia D, Schmid H, Borg M, Riel H, Schenk A (2016) Lateral InAs/Si p-type tunnel FETs integrated on Si—part 2: simulation study of the impact of interface traps. IEEE Trans Electron Dev 63:4240–4247

Saurabh S, Kumar MJ (2011) Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. IEEE Trans Electron Dev 58:404–410

Shekhar S, Madan J, Chaujar R (2018) Source/gate material-engineered double gate TFET for improved RF and linearity performance: a numerical simulation. Appl Phys A 124:739

SILVACO I (2011) ATLAS User’s Manual Santa Clara, CA, Ver 5

Singh PK, Baral K, Kumar S, Chander S, Tripathy MR, Singh AK, Jit S (2020) Source pocket engineered underlap stacked-oxide cylindrical gate tunnel FETs with improved performance: design and analysis. Appl Phys A 126:166

Trabzon L, Awadelkarim O (1998) Damage to n-MOSFETs from electrical stress relationship to processing damage and impact on device reliability. Microelectron Reliab 38:651–657

Tura A, Zhang Z, Liu P, Xie Y-H, Woo JC (2011) Vertical silicon pnpn tunnel nMOSFET with MBE-grown tunneling junction. IEEE Trans Electron Dev 58:1907–1913

Villalon A, Le Carval G, Martinie S, Le Royer C, Jaud M-A, Cristoloveanu S (2014) Further insights in TFET operation. IEEE Trans Electron Dev 61:2893–2898

Wang P-F et al (2004) Complementary tunneling transistor for low power application. Solid State Electron 48:2281–2286

Wei S, Zhang G, Geng L, Shao Z, Yang C-F (2018) Comparison of the performance improvement for the two novel SOI-tunnel FETs with the lateral dual-gate and triple-gate. Microsyst Technol. https://doi.org/10.1007/s00542-018-4018-8

Zhang Z et al (2005) Integration of dual metal gate CMOS on high-k dielectrics utilizing a metal wet etch process. Electrochem Solid State Lett 8:G271–G274

Acknowledgements

Authors would like to thank Microelectronics Research Lab, Department of Applied Physics, Delhi Technological University and all members of VLSI Center of Excellence at Chitkara University for their support in this work.

Author information

Authors and Affiliations

Corresponding authors

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Madan, J., Pandey, R., Sharma, R. et al. Investigation of electrical/analog performance and reliability of gate metal and source pocket engineered DG-TFET. Microsyst Technol 27, 4073–4085 (2021). https://doi.org/10.1007/s00542-020-04845-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-020-04845-2