Abstract

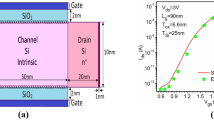

Due to various kind of Band-To-Band Tunneling (BTBT) operation, Heterojunction Tunnel Field Effect Transistors (HEFETs) are widely used in ultralow power applications. Anyhow, circuit complexity is a major issue in case of HEFET based memory development because of their uncomfortable size. Device scaling is a better way to eliminate such kind of issues for HEFET based memory development. Thus, development of Gate-oxide Overlapped Source-HEFET (GOS-HEFET) with lower Subthreshold Swing (SS) based Silicon on Insulator (SOI) is proposed to achieve perfect scaling in this work. Tunneling operation is done with the help of Si-based tunnel devices which are considerably lower than that of MOSFETs. Tunneling rate is enhanced by small bandgap material (Germanium (Ge)) in the source (S) while the ambipolar leakage is minimized by wide band gap material (Silicon (Si)) in the channel. Here, Ge is mainly utilized to dope the source region of P type transistor while Si is used to dope the drain (D) region of N type transistor. Moreover, the tunneling rate of BTBT is enhanced by the geometric alignment of the P and N type transistors with the gate oxide/semiconductor interface. Based on this procedure, five different kinds of SRAM (6 T, 7 T, 8 T, 9 T and 10 T) memory cells are designed. The proposed GOS-HEFET with lower SS on SOI design is implemented using SILVACO TCAD and TANNER CMOS technology. Then, power performance for different temperatures of the proposed method is compared with conventional HEFET based SRAM memory cells.

Similar content being viewed by others

References

Tummala, R.R. (2019 February). Moore’s Law for packaging to replace Moore’s Law for ICS. In 2019 Pan Pacific Microelectronics Symposium (Pan Pacific) IEEE, pp. 1–6.

Xiu, L. (2019). Time Moore: Exploiting Moore’s Law from the perspective of time. IEEE Solid-State Circuits Magazine., 11(1), 39–55.

Al-Shadeedi, A., Liu, S., Kaphle, V., Keum, C. M., & Lüssem, B. (2019). Scaling of high-performance organic permeable base transistors. Advanced Electronic Materials., 5(3), 1800728.

Cheng, Z., Yu, Y., Singh, S., Price, K., Noyce, S. G., Lin, Y. C., Cao, L., & Franklin, A. D. (2019). Immunity to contact scaling in MoS2 transistors using in situ edge contacts. Nano Letters., 19(8), 5077–5085.

Hsiung, C.W., Yeh, J.H., Tu, Y.R and Tseng, W.W. (2019). Leadtrend Tech Corp, Power metal-oxide-semiconductor field-effect transistor device with three-dimensional super junction and fabrication method thereof. U.S. Patent Application. 10/269, 897.

Hanna, A. N., & Hussain, M. M. (2019). Tunneling Field Effect Transistors (p. 67). Energy Efficient Computing & Electronics: Devices to Systems.

Wang, Z., Zhong, Y., Chen, C., Ye, L., Huang, Q., Yang, L., Wang, Y. and Huang, R., (2019 May). Ultra-Low Power Hybrid TFET-MOSFET Topologies for Standard Logic Cells with Improved Comprehensive Performance. In 2019 IEEE International Symposium on Circuits and Systems (ISCAS) IEEE, pp. 1–5.

Yun, S., Oh, J., Kang, S., Kim, Y., Kim, J. H., Kim, G., & Kim, S. (2019). F-Shaped Tunnel Field-Effect Transistor (TFET) for the low-power application. Micromachines., 10(11), 760.

Lin, C.H., Tang, C.J., Chen, H.Y and Hsieh, S.W. (2019). United Microelectronics Corp, Tunneling field effect transistor and method for fabricating the same. U.S. Patent Application. 15/821, 860.

Shaikh, M.R.U and Loan, S.A. (2019 March). Simulation Study of a Split-Channel Quad-Gate Tunnel Field-Effect Transistor. In 2019 6th International Conference on Signal Processing and Integrated Networks (SPIN) IEEE, pp. 896–899.

Joshi, G., Sood, N and Saini, I. (2019 June). Comparative Analysis for Optimising On State Current in a Dual Gate TFET. In 2019 3rd International conference on Electronics, Communication and Aerospace Technology (ICECA) IEEE, pp. 111–116.

Müller, A., Şahin, C., Minhas, M. Z., Fuhrmann, B., Flatté, M. E., & Schmidt, G. (2019). Nanoscale tunnel field-effect transistor based on a complex-oxide lateral heterostructure. Physical Review Applied., 11(6), 064026.

Broderick, C.A., Das, S and O’Reilly, E.P. (2019 July). Theoretical analysis of band-to-band tunneling in highly-mismatched semiconductor alloys. In 2019 International Conference on Numerical Simulation of Optoelectronic Devices (NUSOD) IEEE. 107–108.

Bizindavyi, J., Verhulst, A. S., Verreck, D., Sorée, B., & Groeseneken, G. (2019). Large variation in temperature dependence of band-to-band tunneling current in tunnel devices. IEEE Electron Device Letters., 40(11), 1864–1867.

Chavan, T., Dutta, S., Mohapatra, N. R., & Ganguly, U. (2019). Band-to-band tunneling based ultra-energy efficient silicon neuron. Ar Xiv preprint arXiv, 1902, 09726.

Biswas, A., Tomar, S. and Ionescu, A.M. (2018). Ecole Polytechnique Federale de Lausanne (EPFL), Tunnel FET Based Non-Volatile Memory Boosted by Vertical Band-to-Band Tunneling. U.S. Patent Application. 15/641, 472.

Najam, F., & Yu, Y. S. (2019). Impact of quantum confinement on band-to-band tunneling of line-tunneling type L-Shaped tunnel field-effect transistor. IEEE Transactions on Electron Devices., 66(4), 2010–2016.

Ameen, T. A., Ilatikhameneh, H., Fay, P., Seabaugh, A., Rahman, R., & Klimeck, G. (2018). Alloy engineered nitride tunneling field-effect transistor: a solution for the challenge of heterojunction TFETs. IEEE Transactions on Electron Devices., 66(1), 736–742.

Liu, C., Ren, Q., Chen, Z., Zhao, L., Liu, C., Liu, Q., Yu, W., Liu, X., & Zhao, Q. T. (2019). A T-Shaped SOI tunneling field-effect transistor with novel operation modes. IEEE Journal of the Electron Devices Society., 7, 1114–1118.

Ahmad, S., Ahmad, S. A., Muqeem, M., Alam, N., & Hasan, M. (2019). TFET-based robust 7T SRAM cell for low power application. IEEE Transactions on Electron Devices., 66(9), 3834–3840.

Satyanarayana, B. V. M., & Prakash, D. M. (2019). Design, implementation and power analysis of low voltage heterojunction tunnel field effect transistor based basic 6T SRAM Cell. International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN., 8(11), 2278–3075.

Mishra, V., Verma, Y. K., Verma, P. K., & Gupta, S. K. (2018). EMA-based modelling of the surface potential and drain current of dual-material gate-all-around TFETs. Journal of Computational Electronics, 17(4), 1596–1602.

Mishra, V., Verma, Y.K and Gupta, S.K. (2020). Surface potential-based analysis of ferroelectric dual material gate all around (FE-DMGAA) TFETs. International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, e2726.

Cao, W., Sarkar, D., Khatami, Y., Kang, J., & Banerjee, K. (2014). Subthreshold-swing physics of tunnel field-effect transistors. AIP Advances., 4(6), 067141.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Satyanarayana, B.V.V., Prakash, M.D. Design analysis of GOS-HEFET on lower Subthreshold Swing SOI. Analog Integr Circ Sig Process 109, 683–694 (2021). https://doi.org/10.1007/s10470-021-01821-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-021-01821-2