Abstract

STT-MRAM has been recently researched to replace DRAM in order to reduce the cell size and save the leakage power consumption. Although the read operation in STT-MRAM is acceptable in terms of performance and energy consumption, the write operation discourages the adoption of the STT-MRAM as main memory. A promising approach to overcome the poor write operation is to reduce the planar cell size which decreases the retention time, the write latency and the write energy consumption since the change of the cell size requires no additional manufacturing process. However, since refresh is required in the reduced retention time memory just like DRAM, the leakage energy consumption may increase compared with a traditional STT-MRAM with long retention time. This paper solves the buffer mapping problem onto a system with multiple retention time memories for a stream application to minimize the energy consumption. Experimental results show that a system with two or three different retention time STT-MRAMs reduces 45–75 \(\%\) of write energy consumption compared with a single long retention time STT-MRAM.

Similar content being viewed by others

References

Lee EA (1987) Static scheduling of synchronous data flow programs for digital signal processing. IEEE Trans Comput 14:35–590

Hwang H, Oh T, Jung H, Ha S (2006) Conversion of reference code to dataflow model: H.264 encoder case study, 11th Asia and South Pacific design automation conference. ASP-DAC 2006:24–27

Bhattacharyya SS, Eker J, Janneck JW, Lucarz C, Mattavelli M, Raulet M (2011) Overview of the MPEG reconfigurable video coding framework. J Signal Process Syst 63(2):251–263

Lee D, Oh H (2013) A lifetime aware buffer assignment method for streaming applications on DRAM/ PRAM hybrid memory, ACM TECS

Guo X, Ipek E, Soyata T (2010) Resistive computation: avoiding the power wall with low-leakage. ACM, STT-MRAM based computing

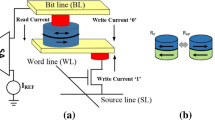

Huai Y (2008) Spin-transfer torque MRAM (STT-MRAM): challenges and prospects. AAPPS Bull 18(6):33–40

Chappert C, Fert A, Dau FNV (2007) The emergence of spin electronics in data storage. Nat Mater 6:813–823

Diao Z et al (2007) Spin-transfer torque switching in magnetic tunnel junctions and spin-transfer torque random access memory. J Phys 19:165209

Sun JZ (2000) Spin-current interaction with a monodomain magnetic body: a model study. Phys Rev B 62:570–578

Raychowdhury A et al. (2009) Design space and scalability exploration of 1T–1STT MTJ memory arrays in the presence of variability and disturbances. In: IEEE international electron devices meeting, pp 1–4

Smullen CW (2011) IV Relaxing non-volatility for fast and energy-efficient STT-RAM caches. In: IEEE 17th international symposium on high performance computer architecture (HPCA)

Diao Z, Li Z, Wang S, Ding Y, Panchula A, Chen E, Wang L-C, Huai Y (2007) Spin-transfer torque switching in magnetic tunnel junctions and spin-transfer torque random access memory. J Phys 19:165209

Sun G et al. (2009) A novel architecture of the 3D stacked MRAM L2 cache for CMPs. High performance computer architecture, 2009. HPCA. In: IEEE 15th international symposium on IEEE, 2009

Chen Y, Cong J, Huang H, Liu C, Prabhakar R, Reinman G (2012) Static and dynamic co-optimizations for blocks mapping in hybrid caches ISLPED, pp 237–242

Li J, Xue CJ, Xu Y (2011) STT-RAM based energy-efficiency hybrid cache for CMPs. In: IEEE 2011 IEEE/IFIP 19th international conference on VLSI and system-on-Chip, pp 31–36

Li J, Shi L, Xue CJ, Yang C, Xu Y (2011) Exploiting set-Level write non-uniformity for energy-efficient NVM-based hybrid cache. In: ESTIMedia IEEE symposium, pp 19–28

Mishra K, Dong X, Sun G, Xie Y, Vijaykrishnan N, Das CR (2011) Architecting on-chip interconnects for stacked 3D STT-RAM caches in CMPs. In: ISCA proceedings of the 38th annual international symposium, pp 69–80

Ahn J, Yoo S, Choi K (2013) Write intensity prediction for energy-efficient non-volatile caches. ISLPED ’13, pp 223–228

Li Q, Li J, Shi L, Zhao M, Xue CJ, He Y (2012) Compiler-assisted STT-RAM-based hybrid cache for energy efficient embedded systems. LCTES ’12 pp 109–118

Qiu K, Zhao M, Fu C, Shi L, Xue CJ (2013) Migration-aware loop retiming for STT-RAM based hybrid cache for embedded systems. ASAP ‘13, pp 83–86

Jog A, Mishra AK, Xu C, Xie Y, Narayanan V, Iyer R, Das CR (2012) Cache revive: architecting volatile STT-RAM caches for enhanced performance in CMPs, DAC ‘12, pp 243–252

Li J, Shi L, Xue CJ, Li Q, Chen Y, He Y (2013) Compiler-assisted refresh minimization for volatile STT-RAM cache, ASP-DAC ‘13, pp 273–278

Rodriguez G, Tourino J, Kandemir MT (2014) Volatile STT-RAM scratchpad design and data allocation for low energy. Technical reports

Li J, Shi L, Li Q, Xue CJ, Chen Y, Xu Y (2013) Cache coherence enabled adaptive refresh for volatile STT-RAM. DATE ‘ 13, pp 1247–1250

Li J, Shi L, Li Q, Xue Chun J, Chen Y, Xu I, Wang Wei (2013) Low-energy volatile STT-RAM cache design using cache-coherence-enabled adaptive refresh, TODAES ’13, 19(5)

Smullen CW, Mohan V, Nigam A, Gurumurthi S, Stan MR (2011) Relaxing non-volatility for fast and energy-efficient STT-RAM caches. In: Proceedings of the 2011 IEEE 17th international symposium on high performance computer architecture, Feb 12–16 2011, p 50–61

Sun Z, Bi X, Li HH, Wong WF, Ong ZL, Zhu X (2011) Multi retention level STT-RAM cache designs with a dynamic refresh scheme. In: proceedings of the 44th annual IEEE/ACM international symposium on microarchitecture

Kultursay E, Kandemir M, Sivasubramaniam A, Mutluy O (2013) Evaluating STT-RAM as an energy-efficient main memory alternative. In: performance analysis of systems and software (ISPASS) IEEE international symposium on 2013

Hosomi M, Yamagishi H, Yamamoto T, Bessho K, Higo Y et al. (2005) A novel non-volatile memory with spin torque transfer magnetization switching: Spin-RAM. In: proceedings of IEDM, pp 459–462

Zhao W, Belhaire E, Mistral Q, Chappert C, Javerliac V et al. (2006) Macro-model of spin-transfer torque based magnetic tunnel junction device for hybrid magnetic-CMOS design. In: IEEE international behavioral modeling and simulation, workshop, pp 40–43

Liu R-S, Yang C-L, Wu W (2012) Optimizing NAND flash-based SSDs via retention relaxation. In: Proceedings of the 10th USENIX conference on file and storage technologies (FAST’12)

Shi L, Qiu K, Zhao M, Xue CJ (2014) Error model guided joint performance and endurance optimization for flash memory. Comput Aided Design of Integr Circuits Syst 33:343–355

Stancu C, Bathen L, Dutt N (2012) Nicolau A. AVid, annotation driven video decoding for hybrid memories. ESTImedia

Oh H, Ha S (2003) Memory-optimized software synthesis from dataflow program graphs with large size data samples. EURASIP J Appl Signal Process 6:514–529

Che W, Chatha K (2011) Scheduling of stream programs onto SPM enhanced processors with code overlay. ESTIMedia

Choi J, Oh H, Kim S, Ha S (2012) Executing synchronous dataflow graphs on an SPM based multi-core architecture, DAC

Bhattacharyya SS, Murthy PK, Lee EA (1997) APGANandRPMC: complementary heuristics for translating DSP block diagrams into efficient software implementations. DAES 2(1):33–60

Gebser M, Kaminski R, Kaufmann B, Ostrowski M, Schaub T, Schneider M (2011) Potassco: The Potsdam Answer Set Solving Collection. AI Communications 24(2):105–124

Cao Y et al. (2000) New paradigm of predictive mosfet and interconnect modeling for early circuit design, IEEE custom Integrated Ckt. Conference http://www-device.eecs.berkeley.edu/ptm, pp 201–204

Oh H, Ha S (2004) Fractional rate dataflow model for efficient code synthesis. J VLSI Signal Process 37:41–51

Acknowledgments

This work was supported by Basic Science Research Programs through the National Research Foundation of Korea (2013R1A1A1013384), and by IT R&D program MKE/KEIT (No. 10041608, Embedded system Software for New-memory based Smart Device).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Choi, K., Oh, H. An energy aware buffer mapping technique on hybrid STT-MRAM memories with multiple retention time for stream applications. Des Autom Embed Syst 17, 693–710 (2013). https://doi.org/10.1007/s10617-014-9147-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10617-014-9147-4