Abstract

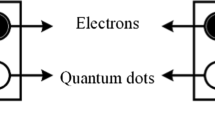

Quantum-dot Cellular automata is a promising area to implement digital systems at nano scale level. Adders and subtractors are widely used in almost every digital information processing system. This work targets to design an efficient 8-bit adder/subtractor that can perform addition as well as subtraction by using a novel control signal distribution scheme. To perform controlled inversion of inputs a novel exclusive-or gate with fewer cells is proposed. During Quantum-dot Cellular automata circuit fabrication, missing cell defects have the potential to affect the performance of a circuit. The proposed designs have higher fault resistance to missing cell defects compared to the existing state-of-the-art designs. Results demonstrate that the proposed design has (N-2) less clock phases compared to the existing state-of-the-art designs. The proposed design can be extended to implement any N-bit adder/subtractor. All the designs are designed and verified using coherence vector simulation engine in QCADesigner.

Similar content being viewed by others

References

Bernstein, K., Cavin, R.K., Porod, W., Seabaugh, A., Welser, J.: Device and architecture outlook for beyond CMOS switches. IEEE Proceedings. 98(12), 2169–2184 (2010)

Cavin, R.K., Lugli, P., Zhirnov, V.V.: Science and engineering beyond Moore’s law. IEEE Proceedings. 100(5), 1720–1749 (2012)

Perri, S., Corsonello, P., Cocorullo, G.: Design of efficient binary comparators in quantum-dot cellular automata. IEEE Trans. Nanotechnol. 13(2), 192–202 (2014a)

Kong, I., Kim, S.W., Swartzlander, E.E.: Design of Goldschmidt dividers with quantum-dot cellular automata. IEEE Trans. Comput. 63(10), 2620–2625 (2014)

Awais, M., Vacca, M., Graziano, M., Roch, M.R., Masera, G.: Quantum dot cellular automata check node implementation for LDPC decoders. IEEE Trans. Nanotechnol. 12(3), 368–377 (2013)

Zhang, M., Cai, L., Yang, X., Cui, H., Feng, C.: Design and simulation of Turbo encoder in quantum-dot cellular automata. IEEE Trans. Nanotechnol. 14(5), 820–828 (2015)

Sheikhfaal, S., Navi, K., Angizi, S., Navin, A.H.: Designing high speed sequential circuits by quantum-dot cellular automata: memory cell and counter study. Quantum Matter. 4(2), 190–197 (2015)

Angizi, S., Sarmadi, S., Sayedsalehi, S., Navi, K.: Design and evaluation of new majority gate-based RAM cell in quantum-dot cellular automata. Microelectron. J. 46(1), 43–51 (2015)

Perri, S., Corsonello, P., Cocorullo, G.: Area-delay efficient binary adders in QCA. IEEE Transactions on very large scale Integration systems. 22(5), 1174–1179 (2014b)

Abedi, D., Jaberipur, G., Sangsefidi, M.: Coplanar full adder in quantum-dot cellular automata via clock-zone based crossover. IEEE Trans. Nanotechnol. 14(3), 497–504 (2015)

Labrado, C., Thapliyal, H.: Design of adder and subtractor circuits in majority logic-based field-coupled QCA nanocomputing. Electron. Lett. 52(6), 464–465 (2016)

Gladshtein, M.: Design and simulation of novel adder/subtractors on quantum-dot cellular automata: radical departure from Boolean logic circuits. Microelectron. J. 44(6), 545–552 (2013)

Hayati, M., Rezaei, A.: Design of novel efficient adder and subtractor for quantum-dot cellular automata. J. Circuit Theory Applications. 43(10), 1446–1454 (2015)

Kianpour, M., Sabbaghi-Nadooshan, R., Navi, K.: A novel design of 8-bitadder/subtractor by quantum-dot cellular automata. J. Comput. Syst. Sci. 80(7), 1404–1414 (2014)

Sangsefidi, M., Karimpour, M., Sarayloo, M.: Efficient Design of a Coplanar Adder/subtractor in quantum-dot cellular automata. IEEE European Modelling Symposium. 456–461 (2015)

Walus, K., Dysart, T.J., Jullien, G.A., Budiman, R.A.: QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 3(1), 26–31 (2004)

SangSefidi, M., Abedi, D., Moradian, M.: Design a collector with more reliability against defects during manufacturing in nanometer technology QCA. J. Softw. Eng. Appl. 6(6), 304–312 (2013)

Gin, A., Tougaw, P.D., Williams, S.: An alternative geometry for quantum-dot cellular automata. J. Appl. Phys. 85(12), 8281–8286 (1999)

Devadoss, R., Paul, K., Balakrishnan, M.: Coplanar qca crossovers. Electron. Lett. 45(24), 1234–1235 (2009)

Arjmand, M.M., Soryani, M., Navi, K.: Coplanar wire crossing in quantum cellular automata using a ternary cell. IET Circuits Devices Systems. 7(5), 263–272 (2013)

Dysart, T.J., Kogge, P.M.: Probabilistic analysis of a molecular quantum-dot cellular automata adder. IEEE International Symposium on Defect and Fault-Tolerance in VLSI Systems. 478–486 (2007)

Shin, S.H., Jeon, J.C., Yoo, K.Y.: Wire-crossing technique on quantum-dot cellular automata, NGCIT, pp. 52–57 (2013)

Janez, M., Pecar, P., Mraz, M.: Layout design of manufacturable quantum-dot cellular automata. Microelectron. J. 43(7), 501–513 (2012)

Lent, C.S., Tougaw, P.D.: A device architecture for computing with quantum dots. IEEE Proceedings. 85(4), 541–557 (1997)

Pudi, V.K., Sridharan, K.: Efficient QCA design of single-bit and multi-bit subtractors. IEEE-NANO. 1155–1158 (2013)

Tahoori, M.B., Huang, J., Momenzadeh, M., Lombardi, F.: Characterization, test, and logic synthesis of and-or-inverter (AOI) gate design for QCA implementation. IEEE Transactions on Computer Aided Design. 24(12), 1881–1893 (2005)

Chabi, A.M., Sayedsalehi, S., Angizi, S., Navi, K.: Efficient QCA exclusive-or and multiplexer circuits based on a Nanoelectronic-compatible designing approach. International Scholarly Research Notices. 2014, 1–9 (2014). https://doi.org/10.1155/2014/463967

Ahmad, F., Bhat, G.M., Khademolhosseini, H., Azimi, S., Angizi, S., Navi, K.: Towards single layer quantum-dot cellular automata adders based on explicit interaction of cells. J. Comput. Sci. 16, 8–15 (2016)

Mohammadi, H., Navi, K.: Energy-efficient single-layer QCA logical circuits based on a novel XOR gate. J. Circuits, Systems and Computers. 27(14), 1850216 (2018). https://doi.org/10.1142/S021812661850216X

Poorhosseini, M., Hejazi, A.R.: A fault-tolerant and efficient XOR structure for modular Design of Complex QCA circuits, Journal of Circuits. Systems and Computers. 27(7), 1850115 (2018). https://doi.org/10.1142/S0218126618501153

Sayedsalehi, S., Azghadi, M.R., Angizi, S., Navi, K.: Restoring and non-restoring array divider designs in quantum-dot cellular automata. Inf. Sci. 311, 86–101 (2015)

Balali, M., Rezai, A.: Design of low-Complexity and High-Speed Coplanar Four-bit Ripple Carry Adder in QCA technology. Int. J. Theor. Phys. 57, 1948–1960 (2018)

Sasamal, T.N., Singh, A.K., Mohan, A.: An efficient design of quantum-dot cellular automata based 5-input majority gate with power analysis. Microprocess. Microsyst. 59, 103–117 (2018). https://doi.org/10.1016/j.micpro.2018.03.002

Sasamal, T.N., Singh, A.K., Mohan, A.: An optimal design of full adder based on 5-input majority gate in coplanar quantum-dot cellular automata. Optik. 127(20), 8576–8591 (2016a)

De, D., Das, J.C.: Design of novel carry save adder using quantum dot-cellular automata. J. Comput. Sci. 22, 54–68 (2017)

Heikalabad, S.R., Asfestani, M.N., Hosseinzadeh, M.: A full adder structure without cross-wiring in quantum-dot cellular automata with energy dissipation analysis. J. Supercomput. 74, 1994–2005 (2018)

Rashidi, H., Rezai, A.: High-performance full adder architecture in quantum-dot cellular automata. IET J. Engineering. 2017(7), 394–402 (2017)

Kassa, S.R., Nagaria, R.K., Karthik, R.: Energy efficient neoteric design of a 3-input majority gate with its implementation and physical proof in quantum dot cellular automata. Nano Communication Networks. 15, 28–40 (2018)

Kumar, D., Mitra, D.: Design of a practical fault-tolerant adder in QCA. Microelectron. J. 53, 90–104 (2016)

Sasamal, T.N., Singh, A.K., Ghanekar, U.: Design of non-restoring binary array divider in majority logic-based QCA. Electron. Lett. 52(24), 2001–2003 (2016b)

Zhang, Y., Xie, G., Sun, M., Lv, H.: Design of normalised and simplified FAs in quantum-dot cellular automata. IET J. Engineering. 2017(10), 557–565 (2017)

Balali, M., Rezai, A., Balali, H., Rabiei, F., Emadi, S.: Towards coplanar quantum-dot cellular automata adders based on efficient three-input XOR gate. Results in Physics. 7, 1389–1395 (2017)

Adelnia, Y., Rezai, A.: A novel adder circuit design in quantum-dot cellular automata technology. Int. J. Theor. Phys. 58(1), 184–200 (2019)

Momenzadeh, M., Huang, J., Tahoori, M., Lombardi, F.: On the evaluation of scaling of QCA devices in the presence of defects at manufacturing. IEEE Trans. Nanotechnol. 4(6), 740–743 (2005)

Walus, K., Jullien, G.A., Dimitrov, V.S.: Computer arithmetic structures for quantum cellular automata. Asilomar Conference on Signals, Systems & Computers. 1435–1439 (2003)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Raj, M., Gopalakrishnan, L. & Ko, SB. Fast Quantum-Dot Cellular Automata Adder/Subtractor Using Novel Fault Tolerant Exclusive-or Gate and Full Adder. Int J Theor Phys 58, 3049–3064 (2019). https://doi.org/10.1007/s10773-019-04184-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10773-019-04184-7