Abstract

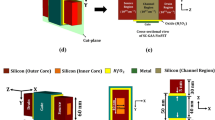

A new heteromaterial planar-gate superjunction insulated-gate bipolar transistor (HG IGBT) is proposed herein. It consists of stepped gate oxides with thickness of 50 nm, 100 nm, and 150 nm. The gate of the proposed structure is constructed using two materials with different workfunction in a triple-segment polygate configuration, connected via metal on the top. The first and last segment consist of the higher-workfunction material (\(P^{+}\) poly) while the mid segment is formed by a lower-workfunction material (\(N^{+}\) poly). The first \(P^{+}\) poly gate near the emitter with a thin (50 nm) oxide layer enables better control over charge carriers in the channel. In addition, the last \(P^{+}\) poly gate with a thicker (150 nm) oxide layer results in a reduction of the gate-to-collector capacitance. Technology computer-aided design (TCAD) simulation results show that the proposed device offers a 23%, 58%, and 22% reduction in the area-specific on resistance (\(R_{{\mathrm {on}}} \cdot A\)), switching delay, and turn-off time, respectively. Additionally, the device exhibits a 44.4% improvement in the peak transconductance for given breakdown voltage (BV). Furthermore, the off-state energy loss and on-state voltage drop are reduced by 38% and 22%, respectively. It is also observed that the proposed device offers an improved figure of merit (FOM) as compared with the conventional structure.

Similar content being viewed by others

References

Yamamoto, T., Fukunaga, Y., Ikoma, D., Miyaoku, Y., Miura-Mattausch, M.: Compact modeling of advanced Si-IGBT for circuit design. In: International Symposium on Devices, Circuits and Systems (ISDCS), pp. 1–6 (2018)

Fujihira, T.: Theory of semiconductor superjunction devices. Jpn. J. Appl. Phys. 36(10), 6254 (1997)

Rajabi, S., Mandal, S., Ercan, B., Li, H., Laurent, M.A., Keller, S., Chowdhury, S.: A demonstration of nitrogen polar gallium nitride current aperture vertical electron transistor. IEEE Electron Dev. Lett. 40(6), 885–888 (2019)

Saremi, M., Hathwar, R., Dutta, M., Koeck, F.A.M., Nemanich, R.J., Chowdhury, S., Goodnick, S.M.: Analysis of the reverse IV characteristics of diamond-based PIN diodes. Appl. Phys. Lett. 111(4), 043507 (2017)

Saremi, M.: Modeling and simulation of the programmable metallization cells (PMCs) and diamond-based power devices. Arizona State University, Tempe, AZ, USA (2017). (Ph.D. Thesis)

Saremi, M., Saremi, M., Niazi, H., Saremi, M., Goharrizi, A.Y.: SOI LDMOSFET with up and down extended stepped drift region. J. Electron. Mater. 46(10), 5570–5576 (2017)

Moghadam, H.A., Dimitrijev, S., Han, J., Haasmann, D., Aminbeidokhti, A.: Transient-current method for measurement of active near-interface oxide traps in 4H-SiC MOS capacitors and MOSFETs. IEEE Trans. Electron Dev. 62(8), 2670–2674 (2015)

Baliga, B.J., Adler, M.S., Love, R.P., Gray, P.V., Zommer, N.D.: The insulated gate transistor: a new three-terminal mos-controlled bipolar power device. IEEE Trans. Electron Dev. 31(6), 821–828 (1984)

Baliga, B.J.: The IGBT Device: Physics, Design and Applications of the Insulated Gate Bipolar Transistor. William Andrew, Amsterdam (2015)

Huang, M., Gao, B., Yang, Z., Lai, L., Gong, M.: A carrier-storage-enhanced superjunction IGBT with ultralow loss and on-state voltage. IEEE Electron Dev. Lett. 39(2), 264–267 (2018)

Iwamuro, N., Laska, T.: Igbt history, state-of-the-art, and future prospects. IEEE Trans. Electron Dev. 64(3), 741–752 (2017)

Hsieh, A.P.S., Camuso, G., Udrea, F., Ng, C., Tang, Y., Vytla, R.K., Ranjan, N., Charles, A.: Superjunction IGBT vs. FS IGBT for 200 C operation. In: IEEE 27th international symposium on power semiconductor devices and IC’s (ISPSD), pp. 137–140 (2015)

Antoniou, M., Udrea, F., Bauer, F.: The superjunction insulated gate bipolar transistor optimization and modeling. IEEE Trans. Electron Dev. 57(3), 594–600 (2010)

Oh, K.H., Kim, J., Seo, H., Jung, J., Kim, E., Kim, S.S., Yun, C.: Experimental investigation of 650V superjunction IGBTs. In: Proceedings of the 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), pp. 299–302 (2016)

Antoniou, M., Lophitis, N., Udrea, F., Bauer, F., Vemulapati, U.R., Badstuebner, U.: On the investigation of the anode side superjunction igbt design concept. IEEE Electron Dev. Lett. 38(8), 1063–1066 (2017)

Antoniou, M., Udrea, F., Bauer, F., Nistor, I.: The semi-superjunction IGBT. IEEE Electron Dev. Lett. 31(6), 591–593 (2010)

Vaidya, M., Naugarhiya, A., Verma, S.: Trench IGBT with stepped doped collector for low energy loss. Semicond. Sci. Technol. 35(2), 025015 (2020)

Gupta, N., Naugarhiya, A.: 1.4 kV Planar gate superjunction igbt with stepped doping profile in drift and collector region. Silicon (2020). https://doi.org/10.1007/s12633-020-00456-8

Sithanandam, R., Kumar, M.J.: Linearity and speed optimization in SOI LDMOS using gate engineering. Semicond. Sci. Technol. 25(1), 015006 (2009)

Saxena, R.S., Kumar, M.J.: A stepped oxide hetero-material gate trench power MOSFET for improved performance. IEEE Trans. Electron Dev. 56(6), 1355–1359 (2009)

Gupta, N., Singh, S., Naugarhiya, A.: An insulated gate bipolar transistor with three-layer poly gate for improved figure of merit. J. Mater. Sci. Mater. Electron. 31(18), 15513–15521 (2020)

Nautiyal, P., Naugarhiya, A., Verma, S.: Workfunction engineered stepped gate SJ UMOS with reduced specific resistance for high speed applications. Semicond. Sci. Technol. 34(9), 095016 (2019)

Saxena, R.S., Kumar, M.J.: Dual-material-gate technique for enhanced transconductance and breakdown voltage of trench power MOSFETs. IEEE Trans. Electron Dev. 56(3), 517–522 (2009)

Khanna, V.K.: Insulated gate bipolar transistor IGBT theory and design. Wiley, Hoboken (2004)

Minato, T., Nitta, T., Uenisi, A., Yano, M., Harada, M., Hine, S.: Which is cooler, trench or multi-epitaxy? Cutting edge approach for the silicon limit by the super trench power MOS-FET (STM). In: Proceedings of the 12th International Symposium on Power Semiconductor Devices ICs (Cat. No.00CH37094), pp. 73–76 (2000)

Udrea, F., Deboy, G., Fujihira, T.: Superjunction power devices, history, development, and future prospects. IEEE Trans. Electron Dev. 64(3), 713–727 (2017)

Xing, H., Dora, Y., Chini, A., Heikman, S., Keller, S., Mishra, U.K.: High breakdown voltage AlGaN-GaN HEMTs achieved by multiple field plates. IEEE Electron Dev. Lett. 25(4), 161–163 (2004)

SILVACO, I.: ATLAS Users Manual, Santa Clara, CA, Ver, 5 (2011)

Nadda, K., Kumar, M.J.: Vertical bipolar charge plasma transistor with buried metal layer. Sci. Rep. 5, 7860 (2015)

Huang, J., Huang, H., Lyu, X., Chen, X.B.: Simulation study of a low switching loss FD-IGBT with high \(dI/dt\) and \(dV/dt\) controllability. IEEE Trans. Electron Dev. 65(12), 5545–5548 (2018)

Bauer, F.D.: The super junction bipolar transistor: a new silicon power device concept for ultra low loss switching applications at medium to high voltages. Solid State Electron. 48(5), 705–714 (2004)

Kumar, M.J., Sithanandam, R.: Extended-\(p^{+}\) stepped gate LDMOS for improved performance. IEEE Trans. Electron Dev. 57(7), 1719–1724 (2010)

Na, K.Y., Kim, Y.S.: Silicon complementary metal-oxide-semiconductor field-effect transistors with dual work function gate. Jpn. J. Appl. Phys. 45(12R), 9033 (2006)

Dash, S., Sahoo, G.S., Mishra, G.P.: Subthreshold swing minimization of cylindrical tunnel FET using binary metal alloy gate. Superlattices Microstruct. 91, 105–111 (2016)

Sumitomo, M., Sakane, H., Arakawa, K., Higuchi, Y., Matsui, M.: Injection control technique for high speed switching with a double gate PNM-IGBT. In: Proceedings of the 25th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), pp. 33–36 (2013)

Harada, S., Tsukuda, M., Omura, I.: Optimal double sided gate control of IGBT for lower turn-off loss and surge voltage suppression. In: Proceedings of the 9th International Conference on Integrated Power Electronics Systems, pp. 1–5 (2016)

Zhang, J., Xia, X., Li, Z., Li, W., Shan, Y., Ren, M., Zhang, B., Li, Z.: A novel high performance enhanced-planar IGBT with P-type buried layer. Int. Conf. Commun. Circ. Syst. (ICCCAS) 1, 327–330 (2013)

Huang, S., Sheng, K., Udrea, F., Amaratunga, G.A.J.: A dynamic n-buffer insulated gate bipolar transistor. Solid State Electron. 45(1), 173–182 (2001)

Zhong, C.W., Hong, L.Z., Bo, Z., Min, R., Ping, Z.J., Yong, L., Ji, L.Z.: A snapback suppressed reverse-conducting IGBT with uniform temperature distribution. Chin. Phys. B 23(1), 018505 (2013)

Antoniou, M., Udrea, F., Bauer, F., Nistor, I.: A new way to alleviate the RC IGBT snapback phenomenon: the super junction solution. In: Proceedings of the 22nd International Symposium on Power Semiconductor Devices and IC’s (ISPSD), pp. 153–156 (2010)

Mori, M., Oyama, K., Arai, T., Sakano, J., Nishimura, Y., Masuda, K., Saito, K., Uchino, Y., Homma, H.: A planar-gate high-conductivity IGBT (HiGT) with hole-barrier layer. IEEE Trans. Electron Dev. 54(6), 1515–1520 (2007)

Baliga, B.J.: Fundamentals of Power Semiconductor Devices. Springer, New York (2010)

Chu, K.W., Lee, W.S., Cheng, C.Y., Huang, C.F., Zhao, F., Lee, L.S., Chen, Y.S., Lee, C.Y., Tsai, M.J.: Demonstration of lateral IGBTs in 4H-SiC. IEEE Electron Dev. Lett. 34(2), 286–288 (2013)

Donlon, J.F., Motto, E.R., Takahashi, T., Fujii, H., Satoh, K.: Chip improvements for future IGBT modules. In: IEEE Industry Applications Society Annual Meeting, pp. 1–7 (2008)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gupta, N., Naugarhiya, A. The design of a new heterogate superjunction insulated-gate bipolar transistor. J Comput Electron 20, 883–891 (2021). https://doi.org/10.1007/s10825-021-01662-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-021-01662-2