Abstract

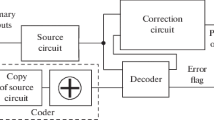

We present two design methods that produce concurrently testable and cascadable combinational blocks for a given logic function. In the first method, the designed block is strongly fault-secure and code-disjoint. Any unordered coding scheme can be used for the input and output. The second method produces designs that are strongly fault-secure and strongly code-disjoint. Here the encoding requires some simple density properties that are seen to be satisfied by the commonly used coding schemes. This makes the method applicable to a larger class of coding schemes than the existing methods. We also show that our designs have lower hardware overhead.

Similar content being viewed by others

References

W.C. Carter and P.R. Schneider, “Design of dynamically checked computers,” IFIP 68, 2: 878–883, Edinburg, Scotland, Aug. 1968.

D.A. Anderson, “Design of self-checking networks using coding techniques”, Ph.D. Thesis, University of Illinois at Urbana-Champaign, 1971.

D.A. Anderson and G. Metze, “Design of totally self checking check circuits for m-out-of-n codes,” IEEE Trans. on Computers, C-22 (3): 263–269, March 1973.

S.M. Reddy, “A note on self-checking checkers,” IEEE Trans. on Computers, C-23 (10): 1100–1102, Oct. 1974.

M.A. Marouf and A.D. Friedman, “Efficient design of self-checking checkers for any m-out-of-n code,” IEEE Trans. on Computers, C-27 (6): 482–490, June 1978.

N.K. Jha and J.A. Abraham, “The design of TSC embedded checkers,” Proc. of Intl. Symp. on Fault Tolerant Computing, FTCS-14, pp. 265–270, 1984.

D.L. Tao, P.K. Lala, and C.R.P. Hartmann, “Three-level totally self-checking checker for l-out-of-n code,” Proc of Intl. Symp. on Fault Tolerant Computing, FTCS-17, pp. 108–113, 1987.

A.M. Paschalis, D. Nikolos, and C. Halatsis, “Efficient modular design of TSC checkers for M-out-of-2M codes,” IEEE Trans. on Computers, C-37 (3): 301–309, March 1988.

D. Nokolos, A.M. Paschalis, and G. Philokyprou, “Efficient design of totally self-checking checkers for all low cost arithmetic codes,” IEEE Trans. on Computers, C-37 (7): 807–814, July 1988.

Y. Min and J. Li, “Strongly fault secure PLAs and totally self-checking checkers,” IEEE Trans. on Computers, C-37 (7): 863–867, July 1988.

J.E. Smith and G. Metze, “Strongly fault-secure logic networks,” IEEE Trans. on Computers, C-27 (6): 491–499, June 1978.

J.M. Berger, “A note on error detecting codes for asymmetric channels,” Information and Control, 4: 68–73, March 1961.

J.E. Smith, “On separable unordered codes,” IEEE Trans. on Computers, C-33 (8): 741–743, Aug. 1984.

B. Bose, “On unordered codes,” Proc. of Intl. Symp. on Fault Tolerant Computing, FTCS-17, pp. 102–107, 1987.

Guyla Mago, “Monotone functions in seuqential circuits,” IEEE Trans. on Computers, C-22 (10): 928–933, Oct. 1973.

W.K. Fuchs and J.A. Abraham, “A unified approach to concurrent error detection,” Proc. of Intl. Symp. on Fault Tolerant Computing, FTCS-14, pp. 4–9, 1984.

M. Nicholaidis, I. Jansch, and B. Courtois, “Strongly code disjoint checkers,” Proc. Intl. on Symp. on Fault Tolerant Computing, FTCS-14, pp. 16–21, 1984.

T. Nanya and M. Uchida, “A strongly fault-secure and strongly code disjoint realization of combinational circuits,” Proc. Intl. Symp. on Fault Tolerant Computing, FTCS-19, pp. 390–397, 1989.

Voclav Dvorak, “A cascade implementation of digital systems,” Microprocessing and Microprogramming, 20 (3): 151–163, Oct. 1990.

T.T. Hwang, R.M. Owens, and M.J. Irwin, “Exploiting communication complexity for multilevel logic synthesis,” IEEE Trans. on CAD of Integr. Circuits and Systems, 9 (10): 1017–1027, Oct. 1990.

J. Poswig, “Disjoint decomposition of Boolean Functions,” IEE Proceedings-E, Computer and Digital Techniques, 138 (1): 48–56, Jan. 1991.

M. Nicolaidis, “A unified built-in-self-test scheme: UBIST,” Proc. Intl. Symp. on Fault Tolerant Computing, FTCS-18, pp. 157–163, 1988.

J.L.A. Hughes, E.J. McCluskey, and D.J. Lu, “Design of totally self-checking comparators with an arbitrary number of inputs,” Proc. Intl. Symp. on Fault Tolerant Computing, FTCS-13, pp. 169–172, 1983.

S. Kundu and S.M. Reddy, “Embedded totally self-checking checkers: A practical design,” IEEE Design & Test of Computers, pp. 5–12, Aug. 1990.

N.K. Jha, “Design of sufficiently strongly self-checking embedded checkers for systematic and separable codes”, Proc of Intl. Conf. on Computer Design, Cambridge, pp. 120–123, Oct. 1989.

G. Hachtel, R. Jacoby, K. Keutzer, and C. Morrison, “On properties of algebraic transformations and the multifault testability of multilevel logic,” Proc. Intl. Conf. on Computer-Aided Design, Santa Clara, pp. 422–425, 1989.

N.K. Jha and J.A. Abraham, “Technique for efficient MOS implementation of totally self-checking checkers,” Proc. of Intl. Symp. of Fault-Tolerant Computing, FTCS-15, Ann Arbor, pp. 430–435, June 1985.

N.K. Jha, “Strongly fault-secure and strongly self-checking domino-CMOS implementation of totally self-checking circuits,” IEEE Trans. on Computer Aided Design, 9 (3): 332–336, March 1990.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Pagey, S., Sherlekar, S.D. & Venkatesh, G. A methodology for the design of SFS/SCD circuits for a class of unordered codes. J Electron Test 2, 261–277 (1991). https://doi.org/10.1007/BF00135442

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF00135442