Summary

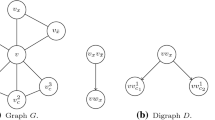

Many reductions among combinatorial problems are known in the context of NP-completeness. These reductions preserve the optimality of solutions. However, they may change the “relative error” of approximative solutions dramatically. In this paper, we apply a new type of reductions, called continuous reductions. When one problem is continuously reduced to another, any approximation algorithm for the latter problem can be transformed into an approximation algorithm for the former. Moreover, the performance ratio is preserved up to a constant factor. We relate the problem “Minimum Number of Inverters in CMOS-Circuits”, which arises in the context of logic synthesis, to several “classical” combinatorial problems such as “Maximum Independent Set” and “Deletion of a Minimum Number of Vertices (Edges) in Order to Obtain a Bipartite (Partial) Subgraph”.

Similar content being viewed by others

References

Brayton, R.K.: Algorithms for Multi Level Logic Synthesis and Optimization. NATO Advanced Study Institute on “Logic Synthesis and Silicon Compilation for VLSI Design”, SSGRR L'Aquila, 1986

Brayton, R.K., Hachtel, G.D., Mcmullen, C.T., Sangiovanni-Vincentelli, A.L.: Logic Minimization Algorithms for VLSI Synthesis. Reading, Mass.: Addison-Wesley 1985

Fleig, W.: Abbildung kombinatorischer Funktionen auf invertierende Mischgatter. (private communications, 1986)

Garey, M.R., Johnson, D.S.: Computers and Intractability, A Guide to the Theory of NP-Completeness. San Francisco: Freeman 1979

Kernighan, B., Lin, S.: An Efficient Heuristic Procedure for Partitioning Graphs. Bell System Technical J. 49, 291–307 (1970)

Lawitsky, G., Klein-Heßling, G.: Architekturbewertung: Implementierungsformen für kombinatorische Schaltungen. (private communications, 1987)

Lawler, E.L., Lenstra, J.K., Rinnooy Kan, A.H.G., Shmoys, D.B.: The Travelling Salesman Problem. A Guided Tour of Combinatorial Optimization. New York: Wiley and Sons 1985

Weste, N., Eshraghian, K.: Principles of CMOS VLSI Design, A Systems Perspective. Reading, Mass.: Addison-Wesley 1985

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Simon, H.U. Continuous reductions among combinatorial optimization problems. Acta Informatica 26, 771–785 (1989). https://doi.org/10.1007/BF00289161

Received:

Issue Date:

DOI: https://doi.org/10.1007/BF00289161