Abstract

Ultra-low power circuit design has received a wide attention due to the fast growth and prominence of portable battery-operated devices with stringent power constraint. Though sub-threshold circuit operation shows huge potential toward satisfying the ultra-low power requirement, it holds challenging design issues. Of these, the increased crosstalk and delay have become serious challenges, particularly for sub-threshold interconnects as integration density increases with every scaled technology node. Consequently, in this paper an analytical approach providing closed form expressions for dynamic crosstalk in coupled interconnects under sub-threshold condition has been proposed. The proposed model is based on the sub-threshold current–voltage expression for a metal-oxide semiconductor transistor. The model determines the propagation delay and timings of the aggressor and victim drivers for the conditions when inputs are switching in-phase and out-of-phase. Subsequently, the transient analysis of dynamic crosstalk is carried out. The comparison of analytical results with SPICE shows that the model captures waveform shape, propagation delay, and timing with good accuracy, with less than 5 % error in timing estimation.

Similar content being viewed by others

References

K. Agarwal, D. Sylvester, D. Blaauw, Modeling and analysis of crosstalk noise in coupled RLC interconnects. IEEE Trans Comput. Aided Des. Integr. Circuits Syst. 25(5), 892–901 (2006)

M. Alioto, Understanding DC behavior of subthreshold CMOS logic through closed-form analysis. IEEE Trans. Circuits Syst. 57(7), 1597–1607 (2010)

J.H. Anderson, F.N. Najm, Low power programmable FPGA routing circuitry. IEEE Trans. Very Large Scale Integr. Syst. 17(8), 1048–1060 (2009)

B.H. Calhoun, A. Chandrakasan, Modeling and sizing for minimum energy operation in subthreshold circuits. IEEE J. Solid State Circuits 40(9), 1778–1786 (2005)

B.H. Calhoun, A. Wang, A. Chandrakasan, Device sizing for minimum energy operation in subthreshold circuits, in Proceedings of the IEEE Custom Integrated Circuits Conference, 2004, pp. 95–98

R. Chandel, S. Sarkar, R.P. Agarwal, Repeater insertion in global interconnects in VLSI circuits. Microelectron. Int. 22(1), 43–50 (2005)

D. Das, H. Rahaman, Crosstalk overshoot/undershoot analysis and its impact on gate oxide reliability in multi-wall carbon nanotube interconnects. J. Comput. Electron. 10(4), 360–372 (2011)

H. Fathabadi, Ultra low power improved differential amplifier. Circuits Syst. Signal Process. 32(2), 861–875 (2013)

S. Ge, E.G. Friedman, Data bus swizzling in TSV-based three-dimensional integrated circuits. Microelectron. J. 44(8), 696–705 (2013)

S.D. Pable, M. Hasan, High speed interconnect through device optimization for subthreshold FPGA. Microelectron. J. 42(3), 545–552 (2011)

S.N. Pu, W.Y. Yin, J.F. Mao, Q.H. Liu, Crosstalk prediction of single- and double-walled carbon-nanotube bundle interconnects. IEEE Trans. Electron Devices 56(4), 560–568 (2009)

S. Subash, J. Kolar, M.H. Chowdhury, A new spatially rearranged bundle of mixed carbon nanotubes as VLSI Interconnection. IEEE Trans. Nanotechnol. 12(1), 3–12 (2013)

K.T. Tang, E.G. Friedman, Delay and power expressions characterizing a CMOS inverter driving an RLC load, in Proceedings of the IEEE Circuits and Systems Symposium, Geneva, 2000, pp. 283–286

A. Wang, B.H. Calhoun, A.P. Chandrakasan, Sub-threshold Design for Ultra Low-Power Systems (Springer, New York, 2006)

S.C. Wong, T.G.Y. Lee, D.J. Ma, Modeling of interconnect capacitance, delay, and crosstalk in VLSI. IEEE Trans. Semicond. Manuf. 13(1), 108–111 (2000)

Predictive Technology Model (PTM), http://ptm.asu.edu. Accessed 14 March 2014

Author information

Authors and Affiliations

Corresponding author

Appendices

Appendix 1

1.1 Output Voltages for Slow Ramp Input Signal: In-Phase Switching

If the active device enters into sub-linear region before the completion of input transition, the input ramp signal is a slow ramp signal. The output voltages of coupled buffers in the time interval \(0\le t\le \varsigma _{n_1 }\) are essentially similar to (8) and (9). At \(\varsigma _{n_1 } \) instant, MN1 leaves the sub-saturation region. MN2 makes transition to sub-linear region of its characteristics at \(t =\varsigma _{n_2 } \). The output voltages of each CMOS buffer in this interval are given by following expressions:

Appendix 2

1.1 Output Voltages for Slow Ramp Input Signal: Out-of-Phase Switching

During the operating condition, \(0\le t \le \varsigma _{\mathrm{p}_2 } \), expressions for the output voltages are same as for fast ramp input, i.e., (41) and (42). At \(t=\varsigma _{p_2 } \), MP2 leaves the sub-saturation and enters into the sub-linear region. In the time limit \(\varsigma _{p_2 } \le t \le \varsigma _{n_1 } \), the output voltages are given by

Appendix 3

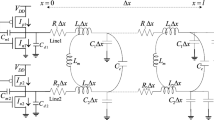

1.1 Estimation of Interconnect Impedance Parasitics

The interconnect impedance parasitics, i.e., resistance and capacitance are presented here and are computed using Ref. [15]. Figure 9 shows the cross-sectional dimensions of interconnect where interconnect is assumed to be placed between two co-planar interconnects and two orthogonal routing planes.

As shown in Fig. 9, if w and h are the width and the height of the interconnect, respectively, s is the separation between two interconnects, \(t \) is the thickness of the dielectric, the interconnect resistance per unit length is given as,

where \(\rho \) stands for the resistivity of the interconnect metal. The interconnect capacitance per unit length is calculated as

where \(\varepsilon \) is the relative permittivity. It consists of the sum of three contributions from left to right: the ideal parallel-plate capacitor, the parallel-plate corner effects, and the sidewall capacitor. The interconnect coupling capacitance per unit length is determined using

Rights and permissions

About this article

Cite this article

Dhiman, R., Chandel, R. Dynamic Crosstalk Analysis in Coupled Interconnects for Ultra-Low Power Applications. Circuits Syst Signal Process 34, 21–40 (2015). https://doi.org/10.1007/s00034-014-9853-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-014-9853-y