Abstract

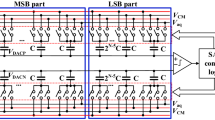

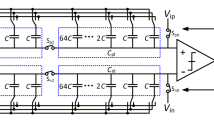

A novel energy-saving and area-efficient tri-level switching scheme is proposed for successive approximation register analog-to-digital converters (SAR ADCs). Different from most published tri-level switching schemes, a new third reference voltage Vaq which equals to 1/4 Vref is applied to the proposed scheme. And benefiting from Vaq, the proposed scheme achieves 87.5% capacitor area reduction over the conventional scheme. Due to the capacitor-splitting structure and top-plate sampling, the switching energy is negative during the first three switching cycles, which means the capacitor arrays return energy back to the reference voltages and results in significant energy saving. For a 10-bit SAR ADC, the average switching energy of proposed scheme is only 5.3 \(CV_{{{\text{ref}}}}^{2}\), which realizes 99.61% energy saving compared with the conventional scheme. Moreover, the proposed scheme is of low control logic complexity since single-side switching is applied during the remaining switching cycles. Therefore, the proposed scheme achieves a good trade-off among energy saving, area efficiency and logic complexity. For a 10-bit SAR ADC, the simulated differential nonlinearity (DNL) and integral nonlinearity (INL) with 1% capacitor mismatch are 0.322 LSB and 0.321 LSB, respectively. Considering 0.3% reference voltage mismatch, the mean values of effective number of bits (ENOB), signal-to-noise-and-distortion ratio (SNDR) and spurious-free-dynamic-range (SFDR) are 9.77 bit, 60.57 dB and 75.43 dB, respectively, through 500 Monte Carlo simulations. To verify the feasibility of circuit implementation, transistor level simulation of a 0.6-V 10-bit 200-KS/s SAR ADC in 40-nm CMOS technology is performed. The ENOB, SNDR and SFDR of SAR ADC with 98.83-kHz Nyquist rate input are 9.66 bit, 59.90 dB and 71.98 dB, respectively.

Similar content being viewed by others

Data Availability

The processed data and material required to reproduce these findings cannot be shared at this time as the data also forms part of an ongoing study.

References

F. Chen, A.P. Chandrakasan, V. Stojanović, A low-power area-efficient switching scheme for charge-sharing DACs in SAR ADCs, in IEEE Custom Integrated Circuits Conference 2010, 19–22 Sept. 2010 2010, pp. 1–4

Y. Chen, Y. Zhuang, H. Tang, A 99.8% energy-reduced two-stage mixed switching scheme for SAR ADC without reset energy. Circuits Syst. Signal Process. 38(12), 5426–5447 (2019). https://doi.org/10.1007/s00034-019-01151-9

B. Ghanavati, E. Abiri, M.R. Salehi, A. Keyhani, A. Sanyal, LSB split capacitor SAR ADC with 99.2% switching energy reduction. Analog Integr Circuits Signal Process. 93(2), 375–382 (2017). https://doi.org/10.1007/s10470-017-1046-8

S. Hsieh, C. Hsieh, A 0.4-V 13-bit 270-kS/s SAR-ISDM ADC With opamp-less time-domain integrator. IEEE J. Solid-State Circuits 54(6), 1648–1656 (2019). https://doi.org/10.1109/JSSC.2019.2894998

Y. Hu, A. Liu, B. Li, Z. Wu, Closed-loop charge recycling switching scheme for SAR ADC. Electron. Lett. 53(2), 66–68 (2017). https://doi.org/10.1049/el.2016.3029

P. Lee, C. Kao, C. Hsieh, A 0.4V 1.94fJ/conversion-step 10b 750kS/s SAR ADC with input-range-adaptive switching, in 2016 IEEE International Symposium on Circuits and Systems (ISCAS), 22–25 May 2016 2016, pp. 1042–1045

J. Lin, C. Hsieh, A 0.3 V 10-bit 1.17 f SAR ADC with merge and split switching in 90 nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 62(1), 70–79 (2015). https://doi.org/10.1109/TCSI.2014.2349571

C. Liu, S. Chang, G. Huang, Y. Lin, A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits 45(4), 731–740 (2010)

J. Liu, S. Liu, L. Huang, Z. Zhu, A highly energy-efficient switching scheme for SAR ADC with the redundant capacitance splitting technology. Analog Integr. Circuits Signal Process. 97(1), 169–176 (2018). https://doi.org/10.1007/s10470-018-1302-6

W. Qu, Z. Zhang, N. Mei, A 99.43% energy saving switching scheme with asymmetric binary search algorithm for SAR ADCs. Circuits Syst. Signal Process. 39(9), 4695–4704 (2020). https://doi.org/10.1007/s00034-020-01383-0

E. Rahimi, M. Yavari, Energy-efficient high-accuracy switching method for SAR ADCs. Electron. Lett. 50(7), 499–501 (2014). https://doi.org/10.1049/el.2013.3451

A. Sanyal, N. Sun, SAR ADC architecture with 98% reduction in switching energy over conventional scheme. Electron. Lett. 49(4), 248–250 (2013). https://doi.org/10.1049/el.2012.3900

M. Sotoudeh, F. Rezaei, A four-level switching scheme for SAR ADCs with 87.5% area saving and 97.85% energy-reduction. Circuits Syst. Signal Proces. 10, 11–12 (2020). https://doi.org/10.1007/s00034-020-01405-x

X. Tong, Y. Zhang, 98.8% switching energy reduction in SAR ADC for bioelectronics application. Electron. Lett. 51(14), 1052–1054 (2015)

H. Wang, W. Xie, Z. Chen, Area-efficient capacitor-splitting switching scheme with a nearly constant common-mode voltage for SAR ADCs. J. Circuits Syst. Comput. 29(10), 2020005 (2019). https://doi.org/10.1142/S0218126620200054

L. Xie, W. Nie, X. Yang, M. Zhou, A group reset method for energy-efficient SAR ADC switching schemes. Analog Integr. Circuits Signal Process. 96(1), 183–187 (2018). https://doi.org/10.1007/s10470-018-1201-x

L. Xie, J. Su, Y. Wang, J. Liu, G. Wen, Switching scheme with 98.4% switching energy reduction and high accuracy for SAR ADCs. Analog Integr. Circuits Signal Process. 90(3), 681–686 (2017). https://doi.org/10.1007/s10470-016-0894-y

B. Yazdani, A. Khorami, M. Sharifkhani, Low-power DAC with charge redistribution sampling method for SAR ADCs. Electron. Lett. 52(3), 187–188 (2016)

T. Yousefi, A. Dabbaghian, M. Yavari, An Energy-Efficient DAC Switching Method for SAR ADCs. IEEE Trans. Circuits Syst. II Express Br. 65(1), 41–45 (2018). https://doi.org/10.1109/TCSII.2017.2676048

C. Yuan, Y. Lam, Low-energy and area-efficient tri-level switching scheme for SAR ADC. Electron. Lett. 48(9), 482–483 (2012). https://doi.org/10.1049/el.2011.4001

Y. Zhang, Y. Li, Z. Zhu, A charge-sharing switching scheme for SAR ADCs in biomedical applications. Microelectron. J. 75, 128–136 (2018). https://doi.org/10.1016/j.mejo.2018.04.003

J. Zhao, N. Mei, Z. Zhang, L. Meng, Vaq-based tri-level switching scheme for SAR ADC. Electron. Lett. 54(2), 66–68 (2018). https://doi.org/10.1049/el.2017.3711

Y. Zhu, C. Chan, U. Chio, S.-W. Sin, U. Seng-Pan, R.P. Martins, F. Maloberti, (2010) A 10-bit 100-MS/s Reference-Free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circuits 45(6), 1111–1121 (2010)

Acknowledgements

This work was supported by the National Natural Science Foundation of China (No. 61871118), the Fundamental Research Funds for the Central Universities (No. 2242019k30037) and the Top-notch Academic Programs Project of Jiangsu Higher Education Institutions (TAPP) (No. PPZY2015B136).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare there is no conflicts of interest regarding the publication of this paper.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Huang, L., Zhang, L., Chen, M. et al. A Low-Energy and Area-Efficient Vaq-Based Switching Scheme with Capacitor-Splitting Structure for SAR ADCs. Circuits Syst Signal Process 40, 4106–4126 (2021). https://doi.org/10.1007/s00034-021-01666-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-021-01666-0