Abstract

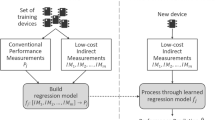

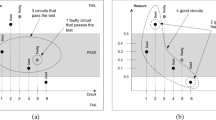

One of the most challenging aspects in nowadays microelectronics industry is production test and verification of mixed-signal circuits. In order to cope with some of the drawbacks encountered in this scenario, researchers have found alternate test as a promising solution in achieving such endeavor. This work prospects the possibilities of using space tessellations along multiple directions in order to improve the test decision boundary definition in the alternate measure space. The proposed method is able to reduce false positive test outcomes, i.e. test escapes, with acceptable penalty in test yield loss metric. The key idea presented in this work is to use an ensemble of octrees, each of them tessellating the plane along different directions. Such tessellations create a refinement in the non linear test decision boundaries without the need of including extra circuit samples. The tree ensemble, together with a strict test decision criterion, serve as a classifier during the production testing phase. The proposed multi-directional ensemble tessellation strategy has been applied to test a band-pass Biquad filter affected by parametric variations. The proposed method has reported promising simulation results in lowering the test escapes metric as compared to a single octree classifier. The computational overhead of evaluating several octrees is insignificant since 2n-tree data structures are traversed efficiently. The octree ensemble technique has also been compared against a classic specification guard-banding technique reporting better test yield loss metrics for the same test escape target.

Similar content being viewed by others

References

Balado L., Lupon E., Figueras J., Roca M., Isern E., Picos R. (2009) Verifying functional specifications by regression techniques on lissajous test signatures. IEEE Trans. Circuits Syst. Regul. Pap. 56(4):754–762

Barragan M., Leger G. (2013) Efficient selection of signatures for analog/rf alternate test. In: 18th IEEE European Test Symposium (ETS), 2013, pp 1–6

Barragan M. J., Leger G. (2015) A procedure for alternate test feature design and selection. IEEE Des. Test 32(1):18–25

Biswas S., Blanton R. D. (2006) Statistical test compaction using binary decision trees. IEEE Des. Test Comput. 23(6):452–462

Bounceur A., Mir S., Stratigopoulos H. -G. (2011) Estimation of analog parametric test metrics using copulas. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 30(9):1400–1410

Chatterjee A., Cherubal S. Method for diagnosing process parameter variations from measurements in analog circuits, June 2002, uS Patent App. 09/838, 404

Cormen T. H., Leiserson C. E., Rivest R. L., Stein C. (2009) Introduction to Algorithms, 3rd edn. MIT Press

Gómez-Pau A., Balado L., Figueras J. (2013) M-S test based on specification validation using octrees in the measure space. In: Proceedings of IEEE European Test Symposium (ETS), Avignon, France, pp 70–75

Gómez-Pau A., Balado L., Figueras J. (2016) EFficient Production Binning Using Octree Tessellation in the Alternate Measurements Space. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 35(8):1386–1395

Gómez-Pau A., Balado L., Figueras J. (2016) Improving indirect test efficiency using multi-directional tessellations in the measure space. In: Proceedings of International Mixed-Signal Testing Workshop (IMSTW). Sant Feliu de Guíxols, Spain

Gómez-Pau A., Balado L., Figueras J. (2016) Indirect test of M-S circuits using multiple specification band guarding. Integr. VLSI J. 55:415–424

International technology roadmap for semiconductors (update), 2015, http://www.itrs2.net

Kendall M. G. (1938) A new measure of rank correlation. Biometrika 30(1/2):81–93

Larguech S., Azaïs F., Bernard S., Comte M., Kerzérho V., Renovell M. (2015) Efficiency evaluation of analog/rf alternate test: Comparative study of indirect measurement selection strategies. Microelectron. J. 46(11):1091–1102

Leger G., Barragan M.J. (2016) Brownian distance correlation-directed search: A fast feature selection technique for alternate test. Integr. VLSI J.:401–414

Meagher D. (1980) Octree encoding: A new technique for the representation, manipulation and display of arbitrary 3-d objects by computer. Rensselaer Polytechnic Institute, New York techreport

Medellin H., Corney J., Davies J., Lim T., Ritchie J. (2008) Octree-based production of near net shape components. IEEE Trans. Autom. Sci. Eng. 5(3):457–466

Milor L. (1998) A tutorial introduction to research on analog and mixed-signal circuit testing. IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process. 45(10):1389–1407

Stopjakova V., Malosek P., Micusik D., Matej M., Margala M. (2004) Classification of defective analog integrated circuits using artificial neural networks. J. Electron. Test. 20(1):25–37

Stratigopoulos H.-G., Makris Y. (2008) Error moderation in low-cost machine-learning-based analog/rf testing. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 27(2):339–351

Stratigopoulos H. G., Mir S. (2012) Adaptive alternate analog test. IEEE Des. Test Comput. 29(4):71–79

Variyam P. N., Chatterjee A. (1998) Enhancing test effectiveness for analog circuits using synthesized measurements. In: Proceedings of the 16th IEEE VLSI Test Symposium, 1998, pp 132–137

Variyam P. N., Chatterjee A. (2000) Specification-driven test generation for analog circuits. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst.:1189–1201

Acknowledgments

This work has been partially supported by the Spanish Ministry of Economy and Competitiveness, projects references TEC2010-18384 and TEC2013-41209-P, and European Union FEDER funds. The authors would like to thank the Reviewers for their helpful improvement comments.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: M. J. Barragan and W. R. Eisenstadt

Rights and permissions

About this article

Cite this article

Gómez-Pau, Á., Balado, L. & Figueras, J. Multi-Directional Space Tessellation to Improve the Decision Boundary in Indirect Mixed-Signal Testing. J Electron Test 33, 315–328 (2017). https://doi.org/10.1007/s10836-017-5648-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-017-5648-y