Abstract

Today, outsourced manufacturing of integrated circuit designs are prone to a range of malicious modifications of the circuitry called Hardware Trojans. HTs can alter the functionality of a circuit, leak secret information and initiate other possible malicious actions. HTs are activated in a very rare condition known by an intruder. Therefore, a group of HT detection methods tries to activate the HT circuitry by crafting test vectors. In this paper, we propose a logic testing based HT detection method using an advised genetic algorithm which creates effective test vectors, the so-called TRIAGE (hardware TR ojan detectI on using an A dvised G enetic algorithm based logic tE sting). The key contribution of this paper is to present a proper fitness function for the genetic algorithm providing better evaluation of the test vectors. The controllability, observability and transition probability factors of rare nodes have been considered in the fitness function. Simulation results indicate 80% reduction in generation time for test sets (on average) as compared to the previous work. On the other hand, reduced generation time for test vectors has been associated with an increase in trigger coverage. The coverage of the TRIAGE method for very hard to trigger Trojans increases by about 23% due to high efficiency of the proposed fitness function for the genetic algorithm.

Similar content being viewed by others

References

Aarestad J, Acharyya D, Rad R, Plusquellic J (2010) Detecting trojans through leakage current analysis using multiple supply pad IDDQs. IEEE Trans Inf Forens Secur 5(4):893–904

Abdellatif KM, Cornesse C, Fournier J, Robisson B (2016) New partitioning approach for hardware Trojan detection using side-channel measurements. In: Bonato V, Bouganis C, Gorgon M (eds) Applied reconfigurable computing, ser. lecture notes in computer science, vol 9625. Springer International Publishing, Cham, pp 171–182. [Online]. Available: http://dl.acm.org/citation.cfm?id=2966541

Ba PS, Dupuis S, Flottes ML, Di Natale G, Rouzeyre B (2016) Using outliers to detect stealthy hardware trojan triggering? In: 2016 1st IEEE International verification and security workshop, IVSW 2016, pp 64–69

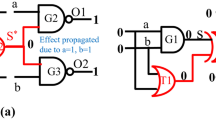

Bazzazi A, Manzuri Shalmani MT, Hemmatyar AMA (2017) Hardware Trojan detection based on logical testing. J Electron Test 33(4):381–395. [Online]. Available: http://link.springer.com/10.1007/s10836-017-5670-0

Bhunia S, Hsiao MS, Banga M, Narasimhan S (2014) Hardware trojan attacks: threat analysis and countermeasures. Proc IEEE 102(8):1229–1247

Chakraborty S, Bhunia RS (2009) Security against hardware Trojan through a novel application of design obfuscation. In: IEEE/ACM International Conference on computer-aided design - digest of technical papers, 2009. ICCAD 2009, pp 113–116

Chakraborty RS, Bhunia S (2009) HARPOON: an obfuscation-based SoC design methodology for hardware protection. IEEE Trans Comput-Aided Des Integr Circ Syst 28(10):1493–1502

Chakraborty RS, Wolff F, Paul S, Papachristou C, Bhunia S (2009) MERO: a statistical approach for hardware Trojan detection. Lecture notes in computer science (including subseries lecture notes in artificial intelligence and lecture notes in bioinformatics), vol 5747 LNCS, pp 396–410

Chakraborty RS, Pagliarini S, Mathew J, Sree Ranjani R, Nirmala Devi M (2017) A flexible online checking technique to enhance hardware Trojan horse detectability by reliability analysis. IEEE Trans Emerg Topics Comput 6750(c):1–1. [Online]. Available: http://ieeexplore.ieee.org/document/7820075/

Goldstein LH, Thigpen EL (1980) SCOAP: Sandia controllability & observability analysis program. In: Proceedings of the seventeenth design automation conference on design automation - DAC ’80. ACM Press, New York, pp 190–196. [Online]. Available: http://portal.acm.org/citation.cfm?doid=800139.804528

Hermawanto D (2013) Genetic algorithm for solving simple mathematical equality problem. Indonesian Institute of Sciences (LIPI). [Online]. Available: arXiv:1308.4675

Keshavarzi A, Roy K, Hawkins CF, De V (2003) Multiple-parameter CMOS IC testing with increased sensitivity for I DDQ. IEEE Trans Very Large Scale Integrat (VLSI) Syst 11(5): 863–870

Li H, Liu Q, Zhang J, Lyu Y (2015) A survey of hardware Trojan detection, diagnosis and prevention. In: 2015 14th International conference on computer-aided design and computer graphics (CAD/Graphics). IEEE, pp 173–180. [Online]. Available: http://ieeexplore.ieee.org/document/7450413/

Liu Y, Jin Y, Nosratinia A, Makris Y (2017) Silicon demonstration of hardware trojan design and detection in wireless cryptographic ICs. IEEE Trans Very Large Scale Integrat (VLSI) Syst 25(4):1506–1519

Mukhopadhyay D, Chakraborty RS (2015) Hardware security design, threats, and safeguards. CRC Press

Narasimhan S, Du D, Chakraborty RS, Paul S, Wolff FG, Papachristou CA, Roy K, Bhunia S (2013) Hardware trojan detection by multiple-parameter side-channel analysis. IEEE Trans Comput 62 (11):2183–2195

Rad R, Plusquellic J, Tehranipoor M (2010) A sensitivity analysis of power signal methods for detecting hardware trojans under real process and environmental conditions. IEEE Trans Very Large Scale Integrat (VLSI) Syst 18(12):1735–1744

Rai D, Lach J (2009) Performance of delay-based trojan detection techniques under parameter variations. In: 2009 IEEE International workshop on hardware-oriented security and trust, HOST 2009, pp 58–65

Rajendran J, Pino Y, Sinanoglu O, Karri R (2012) Logic encryption: a fault analysis perspective. In: Proceedings -design, automation and test in Europe, DATE, pp 953–958. [Online]. Available: http://ieeexplore.ieee.org/document/6176634/

Rajendran J, Pino Y, Sinanoglu O, Karri R (2012) Security analysis of logic obfuscation. In: 2012 Design automation conference (DAC), pp 83–89

Rajendran J, Zhang H, Zhang C, Rose GS, Pino Y, Sinanoglu O, Karri R (2015) Fault analysis-based logic encryption. IEEE Trans Comput 64(2):410–424

Saha S, Chakraborty RS, Nuthakki S, Anshul S, Mukhopadhyay D (2015) Improved test pattern generation for hardware Trojan detection using genetic algorithm and Boolean satisfiability. In: Güneysu T, Handschuh H (eds) Cryptographic hardware and embedded systems – CHES 2015, ser. Lecture notes in computer science, vol 9293. Springer, Berlin, pp 577–596. [Online]. Available: http://link.springer.com/10.1007/978-3-662-48324-4

Salmani H, Tehranipoor M, Plusquellic J (2012) A novel technique for improving hardware trojan detection and reducing trojan activation time. IEEE Trans Very Large Scale Integration (VLSI) Syst 20(1):112–125

Tehranipoor M, Koushanfar F (2010) A survey of hardware trojan taxonomy and detection,10–25

Tehranipoor M, Wang C (2011) Introduction to hardware security and trust. Springer Science & Business Media

Waksman A, Suozzo M, Sethumadhavan S (2013) FANCI : identification of stealthy malicious logic using boolean functional analysis. Ccs 2013(c):697–708

Wolff F, Papachristou C, Bhunia S, Chakraborty RS (2008) Towards Trojan-free trusted ICs: problem analysis and detection scheme. In: Proceedings -design, automation and test in Europe, DATE, pp 1362–1365

Zhang X, Tehranipoor M (2011) Case study: detecting hardware Trojans in third-party digital IP cores. In: 2011 IEEE International symposium on hardware-oriented security and trust, HOST 2011, pp 67–70

Zhang J, Yuan F, Wei L, Liu Y, Xu Q (2015) VeriTrust: verification for hardware trust. IEEE Trans Comput-Aided Des Integrat Circ Syst 34(7):1148–1161

Zhao H, Kwiat K, Kamhoua C, Rodriguez M (2015) Applying chaos theory for runtime hardware Trojan detection. In: 2015 IEEE Symposium on computational intelligence for security and defense applications CISDA 2015 - proceedings, pp 156–161

Zhou B, Zhang W, Srikanthan T, Teo Kian Jin J, Chaturvedi V, Luo T (2015) Cost-efficient acceleration of hardware Trojan detection through fan-out cone analysis and weighted random pattern technique. IEEE Trans Comput-Aided Des Integrat Circ Syst 0070(c):1–1. [Online]. Available: http://ieeexplore.ieee.org/lpdocs/epic03/wrapper.htm?arnumber=7165615

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: C. A. Papachristou

Rights and permissions

About this article

Cite this article

Nourian, M.A., Fazeli, M. & Hely, D. Hardware Trojan Detection Using an Advised Genetic Algorithm Based Logic Testing. J Electron Test 34, 461–470 (2018). https://doi.org/10.1007/s10836-018-5739-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-018-5739-4