Abstract

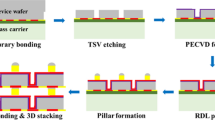

Technological operations involved in manufacturing multilevel ULSI interconnections by the dual damascene (DD) method have been analyzed. Problem issues are considered, including (i) etching of porous intralevel insulation with ultralow values of dielectric constant, (ii) application of metal barrier and seed layers onto the porous surface of etched dielectric spacers, in which copper conductors have to be formed, (iii) low mechanical strength of porous dielectric spacers between copper conductors, (iv) insufficient stability of copper conductors with respect to failures as a result of electromigration, and (v) rapid growth in the resistivity of copper conductors with decreasing width, and limited possibility of compensating this factor by increasing conductor height (thickness). Possible approaches to solving these problems are proposed. According to one of these, horizontal copper conductors are formed first and then a porous dielectric is incorporated into the gaps between conductors by the method of chemical sol-gel deposition from solution by spin-on-dielectric (SOD) method on a centrifuge. The horizontal conductors can then be formed by the standard single-damascene process of copper deposition into temporal mask that is subsequently removed and replaced by the porous dielectric. According to another method, copper conductors are formed by local electrochemical deposition on the wafer surface that is preliminary covered by the barrier layer (BL), seed layer (SL), and a temporal mask, in which a pattern of conductors is prepared by etching down to the SL surface. In this case, the deposited copper conductors initially possess a textured crystalline structure, which facilitates the formation of elongated crystallites during subsequent thermal recrystallization. The surface of conductors can be also covered by local electrochemical process with an electroless barrier layer (e.g., of CoWP). Then, the BL and SL are removed and a porous ultralow-dielectric-constant insulator is incorporated into the gaps between copper conductors. The next stage of forming interconnections in multicrystal ULSIs consists of a three-dimensional (3D) vertical assembly of thinned chips by connecting them with copper conductors formed using through substrate via (TSV) technology. In order to improve heat removal from the assembly and increase its mechanical strength, the filling of vertical through channels in chips by copper is supplemented by copper plating of side edges and the formation of microbumps on crystal surfaces.

Similar content being viewed by others

References

Tzou, J., CoWoS process cuts power, boosts performance, shrinks footprint, Solid State Technol., 2012, vol. 55, no. 9.

Lau, J.H., TSV Interposer: The Most Cost-Effective Integrator for 3D IC Integration, Electronics & Optoelectronics Research Laboratories, Industrial Technology Research Institute.

Reid, J., McKerrow, A., Varadarajan, S., and Kozlowski, G., Copper electroplating approaches for 16 nm technology, Solid State Technol., 2010, vol. 53, no. 5.

Alers, G., 45 nm Reliability Issues, Integration Group, Novellus Systems, AMC-2004, p. 10.

Greer, F. and iALD Group, ALD Technology for Cu B/S Metallic Films, Novellus Systems.

Graham, R.L. et al., Resistivity dominated by surface scattering in sub-50 nm Cu wires, Appl. Phys. Lett., 2010, vol. 96, p. 042116. http://dx.doi.org/10.1063/1.3292022

Gosset, L.G. et al., General Review of Issues and Perspectives for Advanced Copper Interconnections Using Air Gap as Ultra-Low-k Material, IITC, 2003.

Wolf, P.J., Overview of dual damascene Cu/low-k interconnect, International Sematech, August 14, 2003.

Hu, C.-K, Gignac, L.M., Rosenberg, R., et al., Atom motion of Cu and Co in damascene lines with a CoWP cap, Appl. Phys. Lett., 2004, vol. 84, p. 4986.

Peters, L., Exploring advanced interconnect reliability, Semicoductor International, 2002, no. 7.

Peters, L., Achieving superior interconnect reliability at 65 nm and beyond, Semicoductor International, 2006, no. 11.

Peters, L., Better barriers for copper, Semicoductor International, 2006, no. 7.

Singer, P., Controlling copper electromigration, Semicoductor International, 2006, no. 12.

Chih-Chao Yang et al., Co Capping Layers for Cu/Lowk Interconnects IBM Research, 2010.

Semicoductor International, 2009, no. 8.

Koike, J. and Wada, M., Self-forming diffusion barrier layer in Cu-Mn alloy metallization, Appl. Phys. Lett., 2005, vol. 87, p. 041911.

Kudo, H., Haneda, M., Ohtsuka, N., Tabira, T., Sunayama, M., Ochimizu, H., Sakai, H., Owada, T., Kitada, H., and Nara, Y., Ultrathin barrier formation using combination of manganese oxide encapsulation and self-aligned copper silicon nitride barriers for copper wiring in future LSI interconnects, IEEE Trans. Electron Dev., 2011, vol. 58, no. 10, p. 3369.

Lagrange, S. et al., Self-annealing characterization of electroplated copper films, Microelectron. Eng., 2000, vol. 50, p. 449.

Alers, G., 45 nm Reliability Issues, Integration Group, Novellus Systems, AMC-2004.

Tökei, Zs., Gailledrat, T., Li, Y.-L., Schuhmacher, J., Mandrekar, T., Guggilla, S., Mebarki, B., and Maex, K., Barrier reliability of ALD TaN on sub-100 nm copper low-k interconnects.

Ho, P., Rajagopalan, R., Chong, H., Chung. H., and Yu, J., ALD/PVD barrier reduces RC and improves reliability, Semiconductor International, 2004, no. 6.

Valeev, A.S. Krasnikov, G.Ya., et al., A method of manufacturing multilevel copper metallization, RF Patent no. 2420827, 2010.

Valeev, A.S., Krasnikov, G.Ya., and Gvozdev, V.A., A method of manufacturing improved multilevel Cu/ultra-low-K metallization, RF Patent no. 2486632, 2011.

Valeev, A.S., Krasnikov, G.Ya., Gvozdev, V.A, and Kuznetsov, P.I., A method of manufacturing improved multilevel copper metallization with ultra-low-K of intralevel insulation, RF Patent, Application no. 2013155742, 2013.

Turaev, D.Yu., Valeev, A.S., Kruglikov, S.S., and Gvozdev, V.A., Electrolyte and method for copper deposition onto thin conducting sublayer on silicon wafer surface, RF Patent, no. 2510631, 2012.

Jian, J., Lu, Q., Gutmann, R., Thorsten, Matthias, and Lindner, P., Aligned wafer bonding for 3-D interconnect, Semiconductor International, 2005, no. 8.

Mawatari, K., Aoya, K., Umeda, Y., and West, J. A., Protruding TSV tips for enhanced heat dissipation for IC.

Valeev, A.S., Krasnikov, G.Ya., and Mitsyn, N.G., Method of manufacturing crystals with heat-removal elements for vertical 3D (through silicon vias) ULSI assembly, RF Patent Application no. 2013135556, 2013.

Lu, K.H., Xuefeng, Z., Suk-Kyu, R., Jay, I., Rui, H., and Paul, S., Thermo-Mechanical Reliability of 3D ICs Containing through Silicon Vias, Ho Microelectronics Research Center, University of Texas at Austin, Austin, TX 78758.

Baklanov, M.R., de Marneffe, J.-F., Shamiryan, D., Urbanowicz, A.M., Shi, H., Rakhimova, T.V., Huang, H., and Ho, P.S., Plasma processing of low-k dielectrics, J. Appl. Phys., 2013, vol. 113, p. 041101.

Author information

Authors and Affiliations

Corresponding author

Additional information

Original Russian Text © A.S. Valeev, G.Ya. Krasnikov, 2015, published in Mikroelektronika, 2015, Vol. 44, No. 3, pp. 180–201.

Rights and permissions

About this article

Cite this article

Valeev, A.S., Krasnikov, G.Y. Manufacturing technology of intra- and interchip interconnects for modern ULSIs: Review and concepts of development. Russ Microelectron 44, 154–172 (2015). https://doi.org/10.1134/S1063739715030087

Received:

Published:

Issue Date:

DOI: https://doi.org/10.1134/S1063739715030087