Abstract

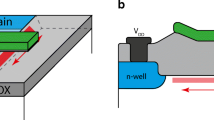

This paper presents an efficient method for mapping a set of Boolean equations onto a set of Static CMOS Complex Gates (SCCGs) under a constraint in the number of serial transistors. This Library Free Technology Mapping (LFTM) approach uses a virtual library of SCCGs available through a layout generator, instead of using a limited set of pre-characterized cells. Our goal is to use a virtual library of SCCGs to perform the mapping at the transistor level, in order to fit the topological constraints imposed by the CMOS technology. Limitations of previously proposed techniques to perform Library Free Technology Mapping are discussed. The proposed method, based on an one-to-one association of CMOS transistors with Binary Decision Diagram arcs, is not dependent on the initial ordering of Boolean equations. Experimental results comparing this technique to previously published ones indicate that it generates good-quality solutions.

Chapter PDF

Similar content being viewed by others

References

Keutzer, K. (1987) DAGON: Technology Binding and Local Optimization by DAG Matching. Proc. of 24th DAC, 341–7.

Detjens, E.; Gannot, G.; Rudell, R.; Sangiovanni-Vinccentelli, A.L. and Wang, A. (1987) Technology mapping in MIS. Proc. of ICCAD, 116–9.

Mailhot, F. and DeMicheli, G. (1993) Algorithms for technology mapping based on binary decision diagrams and on Boolean operations. IEEE Transactions on CAD for IC and Systems, vol. 12, n5, 599–620.

Abouzeid, P.; Leveugle, R.; Saucier, G. and Jamier. R. (1992) Logic synthesis for automatic layout. Proc. of EUROASIC, 146–51.

Berkelaar, M. and Jess, J. (1988) Technology mapping for standard-cell generators. ICCAD, 470–3.

Bryant, R.E. (1986) Graph-based algorithms for Boolean function manipulation. IEEE Transactions on Computers, vol. C-35, n8, 677–91.

Reis, A.; Robert, M.; Auvergne, D. and Reis, R. (1995) Associating CMOS transistors with BDD arcs for technology mapping. IEE Electronics Letters, vol. 31, n14, 1118–20.

Moraes, F.; Azemard, N.; Robert, M. and Auvergne, D. (1993) Flexible Macrocell Layout Generator. 4th ACM/SIGDA Physical Design Workshop, 105–16.

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 1997 Springer Science+Business Media Dordrecht

About this chapter

Cite this chapter

Reis, A.I., Reis, R., Auvergne, D., Robert, M. (1997). Library Free Technology Mapping. In: Reis, R., Claesen, L. (eds) VLSI: Integrated Systems on Silicon. IFIP — The International Federation for Information Processing. Springer, Boston, MA. https://doi.org/10.1007/978-0-387-35311-1_25

Download citation

DOI: https://doi.org/10.1007/978-0-387-35311-1_25

Publisher Name: Springer, Boston, MA

Print ISBN: 978-1-4757-6949-4

Online ISBN: 978-0-387-35311-1

eBook Packages: Springer Book Archive