Abstract

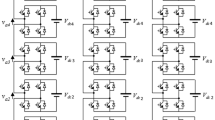

This paper presents, ant colony optimization based hybrid algorithm for selective harmonic elimination in single phase seven level multilevel inverter with reduced switches. For high power and high voltage applications, multilevel structure with selective harmonic elimination (SHE) modulation scheme is used. The output voltage of multilevel inverter contains fundamental component along with harmonics. SHE technique aims to solve non-linear transcendental equations maintaining the fundamental harmonic component to its desired value and to eliminate lower order odd harmonics. Many optimization algorithms have been implemented to solve this problem. But these algorithms are complicated and time consuming. The Newton–Raphson algorithm is also very convergent for solving these non-linear equations. The main disadvantage of this method is, it requires strong initial guess. To overcome these drawbacks, hybrid optimization algorithm is used in this paper. This algorithm is performed in two stages, during first stage ant colony optimization has been run and in second stage the solutions obtained from ACO is used as a initial guess for Newton–Raphson algorithm which confirms the exact converged solution. Thus the drawback of Newton’s method i.e. requirement of good initial guess is overcomed by proposed hybrid algorithm. The MATLAB/SlMULINK software is used for comprehensive simulation of seven-level inverter. Experimental results validate the simulated results.

Similar content being viewed by others

References

Aghdam M, Fathi S, Gharehpetian G (2007) Elimination of harmonics in a multi-level inverter with unequal DC sources using homotopy algorithm. In: Proceedinsg of the IEEE international symposium on industrial electronics, pp 578–583

Banaei MR, Salary E (2010) New multilevel inverter with reduction of switches and gate driver. In: ICEE 2010, pp 11–13

Baskaran J, Thamizharasan S, Rajtilak R (2012) GA based optimization and critical evaluation SHE methods for three level inverters. Int J Soft Comput Eng (IJSCE) 2(3):321–326 (ISSN: 2231-2307)

Chiasson JN, Tolbert LM, McKenzie KJ, Du Z (2003) Control of a multilevel converter using resultant theory. IEEE Trans Control Syst Technol II(3):345–354

Dahidha MSA, Konstantinou G, Agelidis VG (2015) A review of multilevel selective harmonic elimination PWM: formulations, solving algorithms, implementation and applications. IEEE Trans Power Electron 30(8):4091–4106

Edpuganti A, Rathore A (2015) A survey of low switching frequency modulation techniques for medium-voltage multilevel converters. IEEE Trans Ind Electron Soc 5(5):4212–4228

Fei W, Ruan X, Wu B (2009) A generalized formulation of quarter-wave symmetry SHE-PWM problems for multilevel inverters. IEEE Trans Power Electron 24:1758–1766

Franquelo LG, Rodriguez J, Leon JI, Kouro S, Portillo R, Prats MAM (2008) The age of multilevel converters arrives. IEEE Ind Electron Mag 2(2):28–39

Kavousi A, Vahidi B, Salehi R, Kazem M, Farokhnia BN, Fathi SH (2012) Application of the bee algorithm for selective harmonic elimination strategy in multilevel inverters. IEEE Trans Power Electron 27(4):1689–1696

Kouro S, Malinowski M, Gopakumar K, Pou J, Franquelo LG, Wu B, Rodriguez J, Perez MA, Leon JI (2010) Recent advances and industrial applications of multilevel converters. IEEE Trans Ind Electron 57(8):2553–2580

Kumar J, Das B, Agarwal P (2008) Selective harmonic elimination technique for a multilevel inverter. In: NPSC 2008, IIT Bombay, pp 608–613

Meshram PM, Borghate VB (2015) A simplified nearest level control (NLC) voltage balancing method for modular multilevel converter (MMC). IEEE Trans Power Electron 30(I):450–462

Rodrigues J, Lai J, Feng FZ (2002) Multilevel inverters: a survey of topologies controls and applications. IEEE Trans Ind Electron 49(4):724–738

Rodriguez J, Bernet S, Wu B, Pontt JO, Kouro S (2007) Multilevel voltage-source-converter topologies for industrial medium-voltage drives. IEEE Trans Ind Electron 54(6):2930–2945

Sirisukprasert S (1999) Optimized harmonic stepped-waveform for multilevel inverter. M.Sc. thesis, Department of Electrical and Computer Engineering, Virginia Polytechnic Institute and State University (Virginia Tech)

Sundareswaran K, Jayant K, Shanavas TN (2007) Inverter harmonic elimination through a colony of continuously exploring ants. IEEE Trans Ind Electron 54(5):2558–2565

Taghizadeh H, Tarafdar Hagh M (2010) Harmonic elimination of cascade multilevel inverters with nonequal DC sources using particle swarm optimization. IEEE Trans Ind Electron 57(11):3678–3684

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Patil, S.D., Kadwane, S.G. Hybrid optimization algorithm applied for selective harmonic elimination in multilevel inverter with reduced switch topology. Microsyst Technol 24, 3409–3415 (2018). https://doi.org/10.1007/s00542-018-3720-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-018-3720-x