Abstract

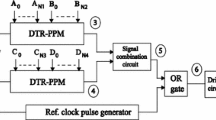

In this paper, the effect of process, voltage and temperature (PVT) variation on the differential-time signaling (DTS) serial link architecture has been studied. An example of 65 nm CMOS 4-bit 6 Gb/s DTS serial link has been designed and simulated using 1.5 GHz as an input clock signal in order to study the effect of PVT variation on DTS architectures. Mont-Carlo simulations have been carried out for the designed link. The simulated link has been tested under different operating temperatures from 0 to 120 °C, the link achieves correct transmission for the temperature range from 0 to 80 °C without calibrating the delay lines against the temperature change. The voltage supply has been varied from 0.95 to 1.05 V in order to study the effect of the voltage supply variation. The simulated link achieves correct transmission for a voltage supply variation within ± 2.5% of the nominal value without calibrating the delay lines against the voltage supply change. Using the DTS architecture as a serial link tolerate an adequate amount of PVT variation as well as relaxes the design constrains of the calibration technique, which is required for the delay lines to ensure correct transmission.

Similar content being viewed by others

References

Bea, W., Yoo, B. -J., & Jeong, D. -K. (2012). Design of CMOS 5 Gb/s 4-PAM transceiver frontend for low-power memory interfave. In IEEE international SoC design conference (ISOCC) (pp. 49–52).

Fukuda, K., et al. (2010). A 12.3 mW 12.5 Gb/s complete transceiver in 65 nm CMOS. In International solid-state circuits conference (ISSCC), San Francisco, USA (pp. 368–369).

Gangasani, G. R., et al. (2014). A 32 Gb/s backplane transceiver with on-chip AC-coupling and low latency CDR in 32 nm SOI CMOS technology. IEEE Journal of Solid-State Circuits (JSSC), 49(11), 2474–2489.

Bulzacchelli, J. F. (2013). Design techniques for CMOS backplane transceivers approaching 30-Gb/s data rates. In IEEE custom integrated circuits conference (CICC), San Jose, CA, USA, 22–25 September 2013 (pp. 1–8).

Kimura, H., et al. (2014). A 28 Gb/s 560 mW multi-standard SerDes with single-stage analog front-end and 14-tap decision feedback equalizer in 28 nm CMOS. IEEE Journal of Solid-State Circuits Journal (JSSC), 49(12), 3091–3103.

Harwood, M. et al., (2012). A 225 mW 28 Gb/s SerDes in 40 nm CMOS with 13 dB of analog equalization for 100GBASE-LR4 and optical transport lane 4.4 applications. In International solid-state circuits conference (ISSCC), San Francisco, USA (pp. 326–327).

Zhang, C., et al. (2013). Multi-channel 5 Gb/s/ch SERDES with emphasis on integrated novel clocking strategies. Journal of Semiconductor Technology and Science, 13(4), 303–317.

Song, B., et al. (2013). A CMOS 7 Gb/s, 4-PAM and 4-PWM, serial link transceiver. IEEE Transaction on Circuits and Systems I, Regular Papers (TCAS-I), 60(2), 457–468.

Ghaderi, N., Ghol, Z., & Fatemi, S. (2016). A CMOS 7 Gb/s, 4-PAM and 4-PWM, serial link transceiver. Analog Integrated Circuits and Signal Processing, 89(3), 809–823.

Rashdan, M. (2017). Dual-time resolution time-based transceiver for low-power serial interfaces. Analog Integrated Circuits and Signal Processing, 92(1), 81–89.

Rashdan, M., Yousif, A., Haslett, J. W., & Maundy, B. (2012). Differential time-signaling data-link architecture. Journal of Signal Processing Systems, 70(1), 21–37.

Rashdan, M., Yousif, A., Haslett, J., & Maundy, B. (2009). A new time-based architecture for serial communication links. In IEEE 16th international conference on electronics Hammamat: Circuits and systems (ICECS) (pp. 531–534).

Townsend, K. (2010). Interference-mitigating TR-UWB receiver. Ph.D. thesis. Calgary, Alberta: University of Calgary.

Sedra, A. S., & Smith, K. C. (2004). Microelectronic circuits (4th ed.). New York: Oxford University Press.

Abidi, A. (2006). Phase noise and jitter in CMOS ring oscillators. IEEE Journal of Solid State Circuits, 41(8), 1803–1816.

Townsend, K. A., Macpherson, A. R., & Haslett, J. (2010). A fine-resolution time-to-digital converter for a 5Gs/s ADC. In IEEE international symposium on circuits and systems (ISCAS) (pp. 3024–3027).

Yousif, A., Rashdan, M., Haslett, J., & Maundy, B. (2008). A low power and high speed ppm design for ultra wideband communications. In The Canadian conference on electrical and computer engineering (CCECE), Niagra falls, Canada (pp. 1055–1058).

Acknowledgements

This work was supported by the provincial iCORE program, by NSERC, and by the University of Calgary.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Rashdan, M. Effect of PVT variations on differential-time signaling data link architecture. Analog Integr Circ Sig Process 99, 71–79 (2019). https://doi.org/10.1007/s10470-018-1304-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-018-1304-4