Abstract

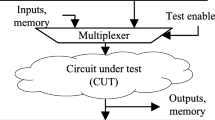

High defect coverage requires good coverage of different fault types. In this paper, we present a comprehensive test vector generation technique for BIST, called Random Single Input Change (RSIC) generation, that can be used to generate tests for many arbitrary misbehaviors that can occur in digital systems, thus providing a single on-chip test generation solution. By proving the effectiveness of universal test sequences produced by such a generation technique in detecting stuck-at, path delay and bridging faults, we demonstrate that using RSIC generation is one of the best and most practical way to reach a high level of defect coverage during BIST of digital circuits.

The original version of this chapter was revised: The copyright line was incorrect. This has been corrected. The Erratum to this chapter is available at DOI: 10.1007/978-0-387-35597-9_40

Chapter PDF

Similar content being viewed by others

References

Semiconductor Industry Association (SIA), “International Technology Roadmap for Semiconductors ( ITRS) ”, 1999 Edition.

Y. Zorian, “Testing the Monster Chip”, IEEE Spectrum, Vol. 36, N° 7, pp. 54–60, 1999.

G. Hetherington et al., “Logic BIST for Large Industrial Designs: Real Issues and Case Studies”, IEEE Int. Test Conf., pp. 358–367, 1999.

J. Rajski and J. Tyszer, “Arithmetic Built-In Self-Test for Embedded Systems”, Prentice Hall PTR, 1998.

R. Dandapani, J. Patel and J. Abraham, “Design of Test Pattern Generators for Built-In Test”, IEEE Int. Test Conf., pp. 315–319, 1984.

C. Fagot, P. Girard and C. Landrault, “On Using Machine Learning for Logic BIST’, IEEE Int. Test Conf., pp. 338–346, 1997.

K. Chakrabarty, B.T. Murray and V. Iyengar, “Built-In Test Pattern Generation for High Performance Circuits Using Twisted-Ring Counters”, VLSI Test Symp., pp. 22–27, 1999.

G. Kiefer; H. Vranken, E.J. Marinissen and H.J. Wunderlich, “Application of Deterministic Logic BIST on Industrial Circuits”, IEEE Int. Test Conf., pp. 105–114, 2000.

W. Wang and S.K. Gupta, “Weighted Random Robust Path Delay Testing of Synthesized Multilevel Circuits”, IEEE VLSI Test Symp., pp. 291–297, 1994.

P. Girard, C. Landrault, V. Moreda and S. Pravossoudovitch, “An Optimized BIST Test Pattern Generator for Delay Testing”, IEEE VLSI Test Symposium, pp. 94–99, 1997.

C. Fagot, O. Gascuel, P. Girard and C. Landrault, “On Calculating Efficient LFSR Seeds for Built-In Self Test”, IEEE European Test Workshop, pp. 7–14, 1999.

A. Vuksic and K. Fuchs, “A New BIST Approach for Delay Fault Testing”, IEEE VLSI Test Symp., pp. 284–288, 1994.

R.C. Aitken, “Nanometer Technology Effects on Fault Models for IC Testing”, IEEE Computer, Vol. 32, N° 11, pp. 46–51, 1999.

P. Nigh et al., “An Experimental Study Comparing the Relative Effectiveness of Functional, Scan, Iddq and Delay Fault Testing”, VLSI Test Symp., pp. 459–464, 1997.

S.C. Ma, P. Franco and E.J. McCluskey, “An Experimental Chip to Evaluate Test Techniques Experiment Results”, IEEE Int. Test Conf., pp. 663–672, 1995.

C.Chen and S.K. Gupta, “BIST Test Pattern Generators for Stuck-Open and Delay Testing”, IEEE Euro. Design & Test Conf.., pp. 289–296, 1994.

A. Virazel, R. David, P. Girard, C. Landrault, and S. Pravossoudovitch, “Delay Fault Testing: Effectiveness of Random SIC and Random MIC Test Sequences”, IEEE European Test Workshop, pp. 9–14, 2000.

M. Abramovici, M. Breuer and A. Friedman, “Digital System Testing and Testable Design”, IEEE Press, Piscataway, NJ, 1990.

K. Mei, “Bridging and Stuck-at Faults”, IEEE Trans. on Computers, Vol. C-23, N° 7, pp. 720–727, 1974.

D. Lavo, B. Chess, T. Larrabee and F. Ferguson, “Diagnosing Realistic Bridging Faults with Single Stuck-at Information”, Trans. on CAD, Vol. C-17, N° 3, pp. 255–267, 1998.

S. Ma, I. Shaik and R. Fetherston, “A Comparison of Bridging Fault Simulation Methods”, IEEE Int. Test Conf., pp. 587–595, 1999.

G.L. Smith, “Model for Delay Faults Based upon Paths”, IEEE Int. Test Conf., pp. 342349, 1985.

A. Krstic and K.T. Cheng, “Delay Fault Testing for VLSI Circuits”, Kluwer Academic Publishers, Boston, 1998.

R. David, “Random Testing of Digital Circuits: Theory and Applications”, Marcel Dekker, Inc., New York, 1998.

R. David, P. Girard, C. Landrault, S. Pravossoudovitch and A. Virazel, “On Hardware Generation of Random Single Input Change Test Sequences”, IEEE European Test Workshop, PP. 117–123, 2001.

P. Girard, C. Landrault, S. Pravossoudovitch and A. Virazel, “Comparison Between Random and Pseudo-Random Generation for BIST of Delay, Stuck-at and Bridging Faults”, IEEE On-Line Testing Workshop, pp. 121–126, 2000.

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2002 IFIP International Federation for Information Processing

About this chapter

Cite this chapter

David, R., Girard, P., Landrault, C., Pravossoudovitch, S., Virazel, A. (2002). Random Adjacent Sequences. In: Robert, M., Rouzeyre, B., Piguet, C., Flottes, ML. (eds) SOC Design Methodologies. IFIP — The International Federation for Information Processing, vol 90. Springer, Boston, MA. https://doi.org/10.1007/978-0-387-35597-9_35

Download citation

DOI: https://doi.org/10.1007/978-0-387-35597-9_35

Publisher Name: Springer, Boston, MA

Print ISBN: 978-1-4757-6530-4

Online ISBN: 978-0-387-35597-9

eBook Packages: Springer Book Archive