Abstract

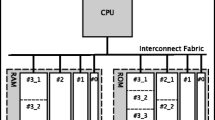

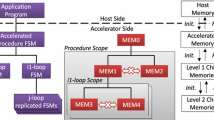

This paper presents a compiler technique that reduces the energy consumption of the memory subsystem, for an off-chip partitioned memory architecture having multiple memory banks and various low-power operating modes for each of these banks. More specifically, we propose an efficient array allocation scheme to reduce the number of simultaneously active memory banks, so that the other memory banks that are inactive can be put to low power modes to reduce the energy. We model this problem as a graph partitioning problem, and use well known heuristics to solve the same. We also propose a simple Integer Linear Programming (ILP) formulation for the above problem. Our approach achieves, on an average, 20% energy reduction over the base scheme, and 8% to 10% energy reduction over previously suggested methods. Further, the results obtained using our heuristic are within 1% of optimal results obtained by using our ILP method.

Chapter PDF

Similar content being viewed by others

Keywords

These keywords were added by machine and not by the authors. This process is experimental and the keywords may be updated as the learning algorithm improves.

References

Lebeck, A.R., et al.: Power aware page allocation. In: Proc. of the Ninth International Conference on Architectural support for programming languages and operating systems, pp. 105–116 (2000)

Athavale, R., et al.: Influence of array allocation mechanisms on memory system energy. In: Proc. of the 15th International Parallel and Distributed Processing Symposium (2001)

Cathoor, F., et al.: System-level transformations for low-power data transfer and storage. In: Chandrakasan, R., Brodersen, R. (eds.) Low- Power CMOS Design, IEEE Press, Piscataway (1998)

Cho, J., Paek, Y., Whalley, D.: Fast memory bank assignment for fixed-point digital signal processors. ACM Transactions on Design Automation of Electronic Systems (TODAES), 52–74 (2004)

Delaluz, V., et al.: Energy-Oriented Compiler Optimizations for Partitioned Memory Architectures. In: Proc. of International conference on Compilers, architecture, and synthesis for embedded systems, pp. 138–147 (2000)

Delaluz, V., et al.: DRAM Energy Management Using Software and Hardware Directed Power Mode Control. In: Proc. of The Seventh International Symposium on High-Performance Computer Architecture (January 2001)

Ford, L.R., Fulkerson, D.R.: Flows in networks, p. 11. Princeton University Press, Princeton (1962)

Hiser, J.D., Davidson, J.W.: EMBARC: an efficient memory bank assignment algorithm for retargetable compilers. ACM SIGPLAN Notices 39(7) (2004)

Karypis, G., Kumar, V.: Multilevel k-way hypergraph partitioning. Technical Report TR 98-036, Department of Computer Science, University of Minnesota (1998)

Kernighan, B.W., Lin, S.: An efficient heuristic procedure for partitioning graphs. The Bell System Technical Journal 49(2), 291–307 (1970)

Livermore Kernels, http://www.netlib.org/benchmark/

lp_solve, http://groups.yahoo.com/group/lp_solve/

Samsung® Electronics - Direct RDRAM DataSheet (2005)

Sarvani, V.V.N.S.: Compiler Techniques for Code Size and Power Reduction for Embedded Processors. M.Sc.[Engg.] Thesis, Department of Computer Science and Automation, Indian Institute of Science, Bangalore, India (2003)

Burger, D., Austin, T.: The SimpleScalar Tool Set, Version 3.0. Technical report, Department of Computer Science, University of Wisconsin, Madison (1999)

Wang, Z., Huw, X.S.: Energy-aware variable partitioning and instruction scheduling for multibank memory architectures. ACM Transactions on Design Automation of Electronic Systems (TODAES), 369–388 (2005)

Wilson, R., et al.: SUIF: An infrastructure for research on parallelizing and optimizing compilers. ACM SIGPLAN Notices 29(12), 31–37 (1994)

Author information

Authors and Affiliations

Editor information

Rights and permissions

Copyright information

© 2007 Springer Berlin Heidelberg

About this paper

Cite this paper

Shyam, K., Govindarajan, R. (2007). An Array Allocation Scheme for Energy Reduction in Partitioned Memory Architectures. In: Krishnamurthi, S., Odersky, M. (eds) Compiler Construction. CC 2007. Lecture Notes in Computer Science, vol 4420. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-71229-9_3

Download citation

DOI: https://doi.org/10.1007/978-3-540-71229-9_3

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-71228-2

Online ISBN: 978-3-540-71229-9

eBook Packages: Computer ScienceComputer Science (R0)